**Centro de Tecnologia e Urbanismo

Departamento de Engenharia Elétrica**

## **Amplificador de áudio tipo classe D, resposta em frequência 20 Hz a 20 kHz, alta fidelidade e modulação multiplexada**

**Rodolfo Barreto Canônico**

**Londrina-PR, fevereiro de 2011.**

# **RODOLFO BARRETO CANÔNICO**

## **Amplificador de áudio tipo classe D, resposta em frequência 20 Hz a 20 kHz, alta fidelidade e modulação multiplexada**

Dissertação de mestrado submetida à

Universidade Estadual de Londrina

como parte dos requisitos para a obtenção

do grau de mestre em Engenharia Elétrica.

Orientador: Prof. Dr. Carlos Henrique Gonçalves Treviso

Londrina, Fevereiro de 2011.

*Dedico este trabalho, em primeiro lugar, a Deus, por ser o autor da vida, Criador de todas as coisas e Pai amoroso. À meus pais, por todo o carinho e compreensão ao longo dos anos, por me formarem e serem os primeiros responsáveis por estar aqui. À todos os que, de alguma forma, estiverem a meu lado, oferecendo carinho, apoio ou alguma ajuda concreta.*

## AGRADECIMENTOS

Agradeço primeiramente à Deus, Criador de todas as coisas, Verdade que se revela diariamente a todos os que o procuram de coração sincero e despojado.

Agradeço aos meus pais, pela formação maravilhosa que me deram, e pelo incentivo para que eu alcançasse meus objetivos. A presença deles sempre é fundamental em minha vida.

Agradeço ao Profº Dr. Carlos Henrique Gonçalves Treviso, orientador deste trabalho, por todo o suporte técnico, ideias, ajuda e conhecimento compartilhados ao longo destes dois anos. Se trilho o caminho para obter o grau de Mestre em Engenharia Elétrica é, fundamentalmente, graças ao trabalho do orientador.

Agradeço aos demais professores do Departamento de Engenharia Elétrica da UEL, pelo apoio e conhecimentos compartilhados ao longo de sete anos de estudo.

Agradeço aos colegas de laboratório, o profº. André Luiz Batista Ferreira, sempre solícito em ajudar nas dificuldades como no auxílio concreto em diversas etapas do trabalho, como aos membros do corpo técnico: Heitor, Emílio, Older, Luiz Mathias e Luis. Muito obrigado pelo prestativo serviço de todos, sempre com muita qualidade, por auxiliar no progresso das pesquisas.

Agradeço aos demais colegas de mestrado: Nelson, André, Luis Guilherme, Osmar, Moanir, Rafael, Yuri e tantos outros, que estiveram presentes em todos os momentos, seja cursando disciplinas, sendo em momentos de descontração no almoço ou em cafés. O apoio e o bom humor de todos foi indispensável para que o trabalho chegasse a esse ponto.

Agradeço à CAPES pelo apoio financeiro em forma de bolsa de estudos, que permitiu a pesquisa em tempo integral.

Agradeço, por fim, a todos os amigos que stiveram ao meu lado ao longo desses anos, dividindo o peso das dificuldades e multiplicando as alegrias. Em especial, agradeço à minha querida Eloísa, companheira fiel dos melhores momentos, e que soube amenizar grande parte das dificuldades por mim encontradas. Seu carinho foi de valor inestimável.

Resumo da dissertação apresentada à UEL como parte dos requisitos necessários para obtenção do grau de mestre em Engenharia Elétrica.

# **Amplificador de áudio tipo classe D, resposta em frequência 20 Hz a 20 kHz, alta fidelidade e modulação multiplexada**

**Rodolfo Barreto Canônico**

FEVEREIRO/2011

Orientador: Carlos Henrique Gonçalves Treviso

Área de Concentração: Eletrônica de Potência

Palavras-chave: Amplificador classe D, Inversor, controle, Modulação PWM, multiplexação

Com o avanço da utilização de dispositivos de mídia portáteis, que utilizam baterias, faz-se necessário o projeto de amplificadores de áudio com rendimento superior aos tradicionalmente utilizados, como amplificadores classe AB. Nesse ínterim, ganham espaço no mercado os amplificadores classe D, por possuirem um elevado rendimento - superior a 90% - e alcançar uma alta fidelidade sonora. Contudo, esta classe de amplificadores utiliza transistores operando com chaveamento, implicando em uma série de dificuldades para alcançar um alto desempenho. Portanto, o trabalho apresenta algumas alternativas para a montagem de um amplificador classe D de alta eficiência, tais como uma nova abordagem do circuito de *driver*, utilizando a técnica da multiplexação, e a consequente montagem de um inversor senoidal bipolar PWM utilizando esta técnica. Também apresenta uma revisão sobre a modulação PWM e sua aplicação em amplificadores de áudio, bem como a forma de realizar a filtragem deste sinal, de modo a conseguir uma alta fidelidade sonora. Também é proposto um circuito de controle altamente versátil, que seja capaz de controlar um inversor em múltiplas aplicações, de amplificadores de áudio à *no breaks*, além de disponibilizar um controle para conversores. São apresentados os protótipos elaborados bem como os resultados obtidos com os mesmos, em variadas condições. É feita a avaliação da THD e do rendimento dos amplificadores, constatando seu alto desempenho e fidelidade para aplicações de áudio.

---

# Conteúdo

---

|                                                                                            |             |

|--------------------------------------------------------------------------------------------|-------------|

| <b>Lista de Figuras</b>                                                                    | <b>viii</b> |

| <b>Lista de Tabelas</b>                                                                    | <b>xiii</b> |

| <b>1 Introdução</b>                                                                        | <b>1</b>    |

| <b>2 Revisão da Literatura</b>                                                             | <b>6</b>    |

| 2.1 Parâmetros importantes no estudo de amplificadores de áudio . . . . .                  | 7           |

| 2.1.1 Distorção . . . . .                                                                  | 7           |

| 2.1.2 Ruído . . . . .                                                                      | 8           |

| 2.2 Amplificadores lineares de potência . . . . .                                          | 9           |

| 2.2.1 Amplificador classe A . . . . .                                                      | 9           |

| 2.2.2 Amplificador classe B . . . . .                                                      | 10          |

| 2.2.3 Amplificador classe AB . . . . .                                                     | 11          |

| 2.3 Amplificador classe D . . . . .                                                        | 11          |

| 2.3.1 Considerações sobre o rendimento e THD . . . . .                                     | 12          |

| 2.3.2 Detalhamento das perdas nos MOSFETs . . . . .                                        | 13          |

| 2.3.3 Topologias inversoras utilizadas: <i>Half Bridge</i> ou <i>Full Bridge</i> . . . . . | 14          |

| 2.3.4 Outras topologias . . . . .                                                          | 14          |

| 2.3.5 Conclusões . . . . .                                                                 | 15          |

| 2.4 A modulação PWM . . . . .                                                              | 16          |

| 2.4.1 Descrição analítica da modulação PWM . . . . .                                       | 19          |

| 2.4.2 Análise da tensão de saída . . . . .                                                 | 21          |

|                                                                             |           |

|-----------------------------------------------------------------------------|-----------|

| <b>3 Desenvolvimento</b>                                                    | <b>23</b> |

| 3.1 Circuito inversor . . . . .                                             | 23        |

| 3.1.1 Descrição do funcionamento do inversor . . . . .                      | 24        |

| 3.1.2 O filtro de saída . . . . .                                           | 29        |

| 3.2 Circuito de controle proposto . . . . .                                 | 31        |

| 3.2.1 Controle do inversor . . . . .                                        | 32        |

| 3.2.2 Controle do conversor DC/DC . . . . .                                 | 35        |

| 3.3 Circuitos auxiliares . . . . .                                          | 37        |

| 3.3.1 Pré-amplificador . . . . .                                            | 37        |

| 3.3.2 Redução e adequação do sinal de tensão na saída do inversor . . . . . | 40        |

| 3.3.3 Limitador da corrente de saída . . . . .                              | 44        |

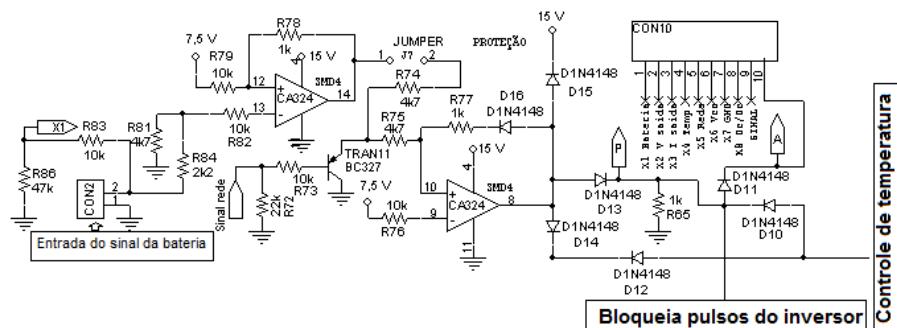

| 3.3.4 Controle de temperatura . . . . .                                     | 45        |

| 3.3.5 Soft start . . . . .                                                  | 46        |

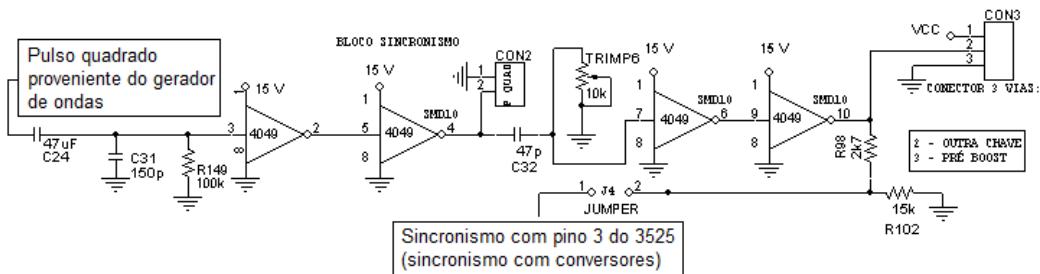

| 3.3.6 Sincronismo . . . . .                                                 | 47        |

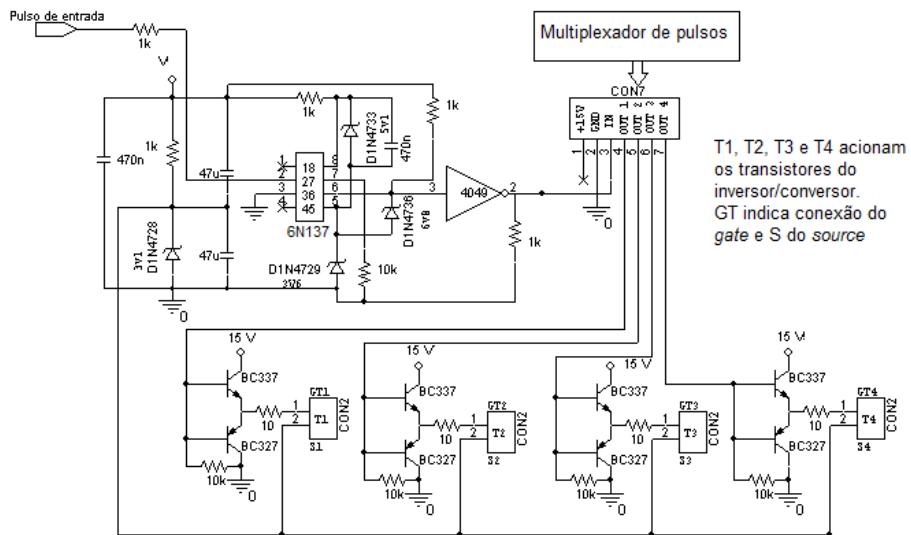

| 3.3.7 Circuito de <i>driver</i> proposto . . . . .                          | 48        |

| 3.3.8 Detecção de presença da rede elétrica . . . . .                       | 52        |

| 3.3.9 Comutação dos conversores . . . . .                                   | 54        |

| 3.3.10 Circuito de proteção . . . . .                                       | 56        |

| 3.4 Circuito de controle - considerações finais . . . . .                   | 57        |

| <b>4 Resultados e discussão</b>                                             | <b>59</b> |

| 4.1 Simulações . . . . .                                                    | 59        |

| 4.1.1 Pré-amplificador . . . . .                                            | 59        |

| 4.1.2 Simulações do inversor . . . . .                                      | 63        |

| 4.2 Resultados experimentais . . . . .                                      | 69        |

| 4.2.1 Circuito de <i>driver</i> . . . . .                                   | 69        |

| 4.2.2 Gerador de ondas triangular e quadrada . . . . .                      | 75        |

| 4.2.3 Circuito de sincronismo . . . . .                                     | 77        |

| 4.2.4 Resultados obtidos com o protótipo completo . . . . .                 | 78        |

| <b>5 Conclusão</b>                                                          | <b>92</b> |

|                                                                                              |            |

|----------------------------------------------------------------------------------------------|------------|

| <b>Bibliografia</b>                                                                          | <b>96</b>  |

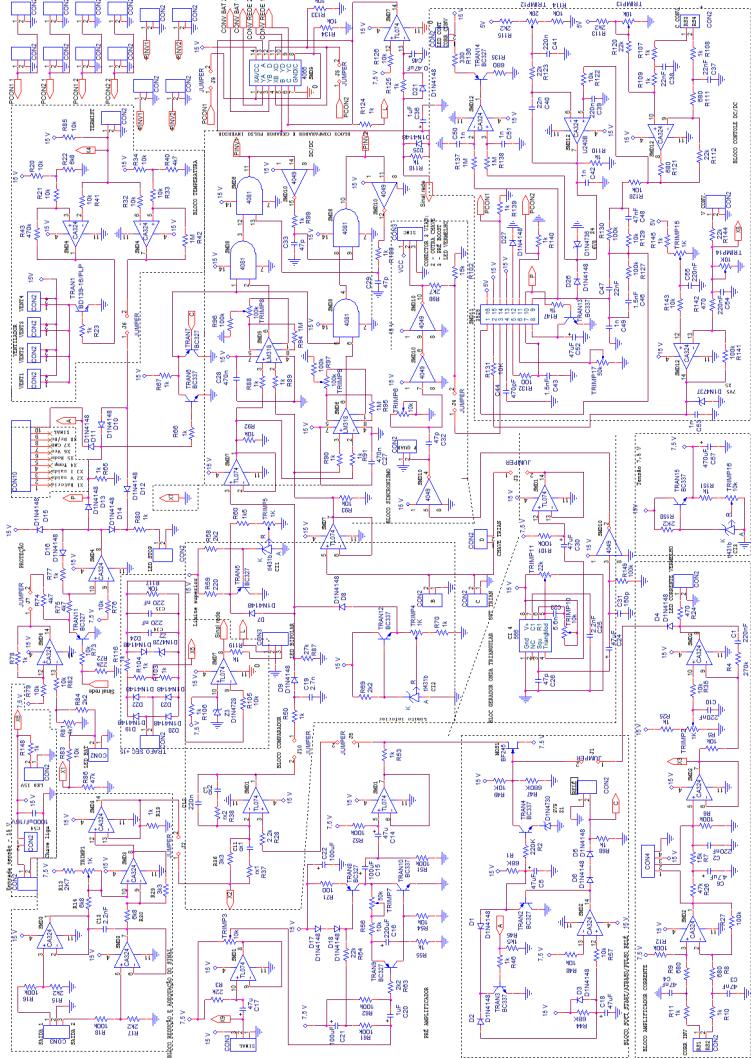

| <b>A Circuito de controle completo</b>                                                       | <b>99</b>  |

| <b>B Projeto do inversor senoidal bipolar multiplexado, <i>snnuber</i> e filtro de saída</b> | <b>100</b> |

| B.1 Cálculo do <i>snnuber</i> . . . . .                                                      | 100        |

| B.2 O filtro de saída . . . . .                                                              | 101        |

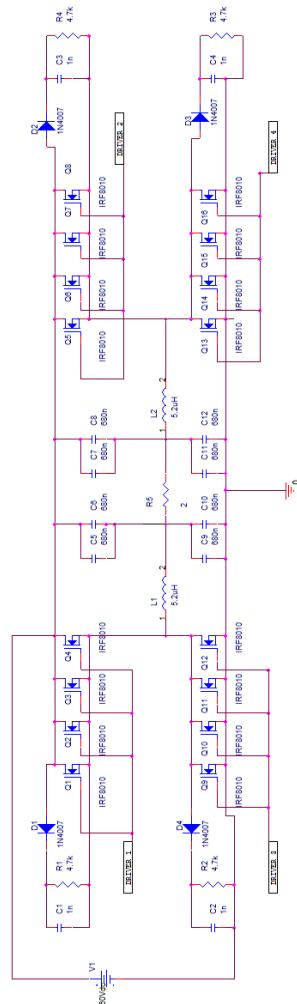

| <b>C Circuito de potência (inversor e filtro)</b>                                            | <b>103</b> |

| <b>D Circuito de <i>driver</i> e multiplexador de pulsos completo</b>                        | <b>104</b> |

---

# Lista de Figuras

---

|      |                                                                               |    |

|------|-------------------------------------------------------------------------------|----|

| 2.1  | Diagrama de blocos para amplificador de áudio classe D proposto. . . . .      | 7  |

| 2.2  | Amplificador classe A. . . . .                                                | 9  |

| 2.3  | Amplificador classe B. . . . .                                                | 10 |

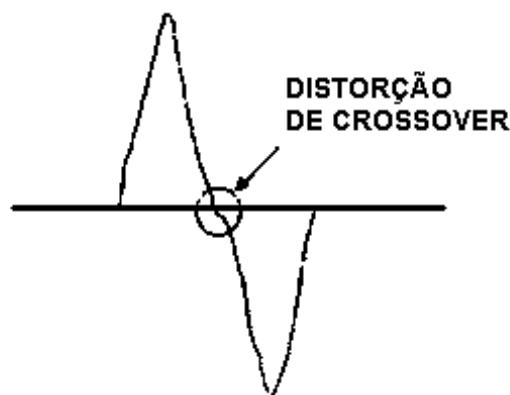

| 2.4  | Distorção de <i>crossover</i> . . . . .                                       | 10 |

| 2.5  | Amplificador classe AB. . . . .                                               | 11 |

| 2.6  | Amplificador classe D. . . . .                                                | 12 |

| 2.7  | (A) Topologia <i>Full Bridge</i> e (B) Topologia <i>Half Bridge</i> . . . . . | 14 |

| 2.8  | Topologia de amplificador classe D - dispensa filtro de saída. . . . .        | 15 |

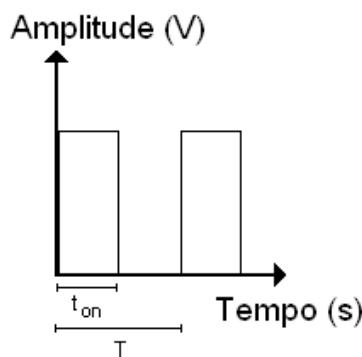

| 2.9  | Pulso quadrado e os parâmetros da razão cíclica. . . . .                      | 16 |

| 2.10 | Esquema de geração e formas de onda da modulação AD, adaptação. . . . .       | 17 |

| 2.11 | Esquema de geração e formas de onda da modulação BD, adaptação. . . . .       | 18 |

| 2.12 | Filtro de saída para modulação AD. . . . .                                    | 19 |

| 2.13 | Filtro de saída para modulação BD. . . . .                                    | 19 |

| 2.14 | Geração de um sinal PWM por meio de modulação senoidal, adaptação. . . . .    | 20 |

| 2.15 | Definição dos instantes de comutação. . . . .                                 | 21 |

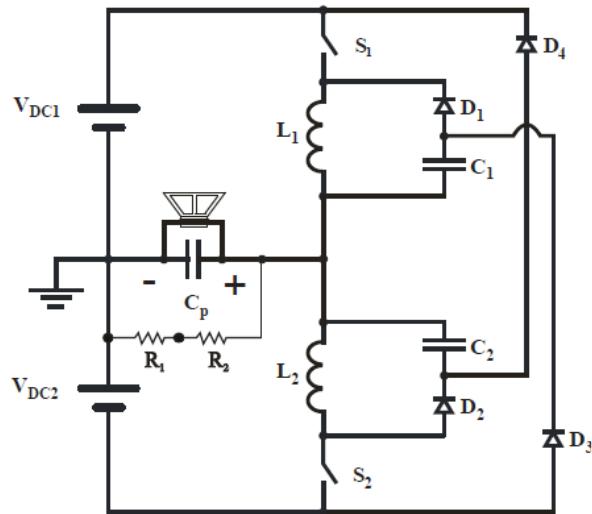

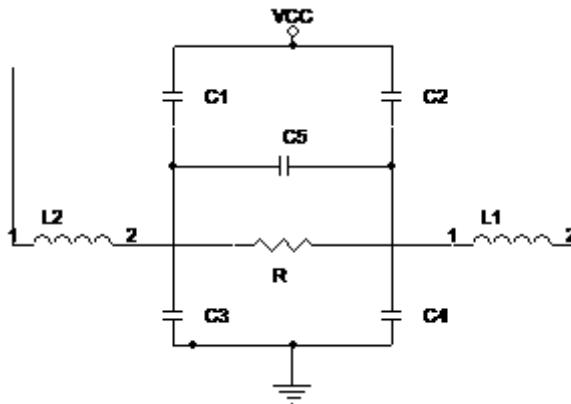

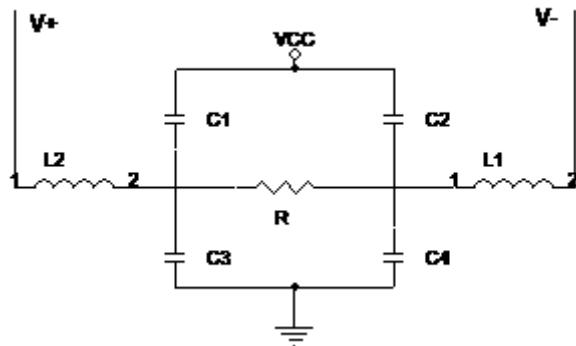

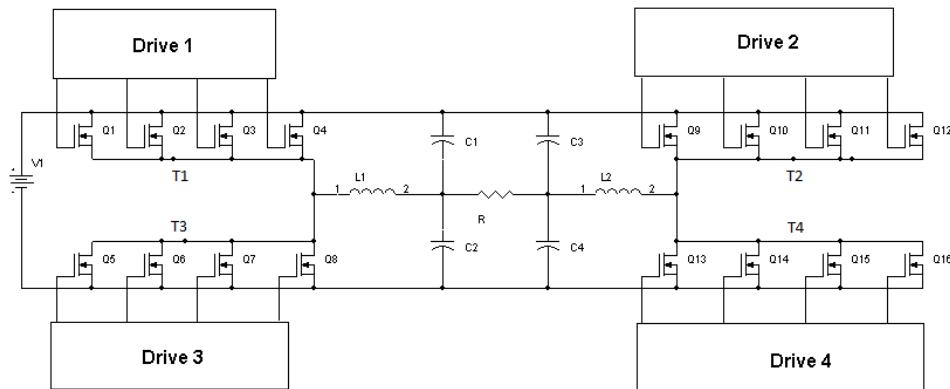

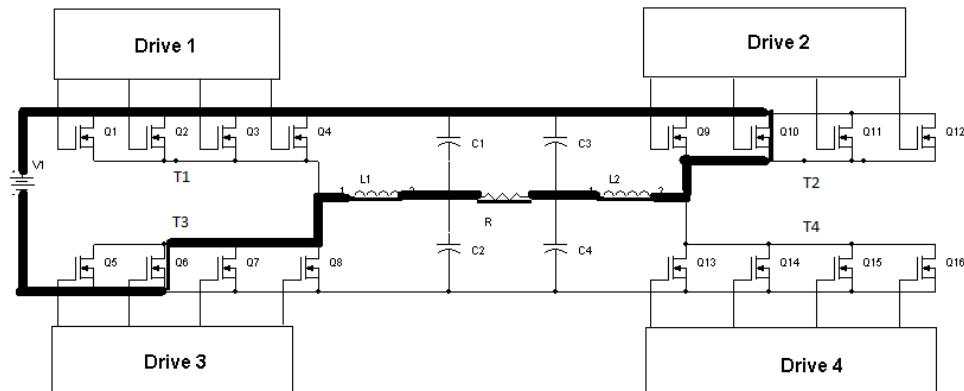

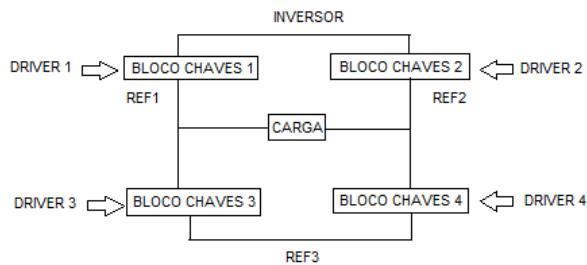

| 3.1  | Inversor senoidal bipolar proposto, com multiplexação nas chaves. . . . .     | 24 |

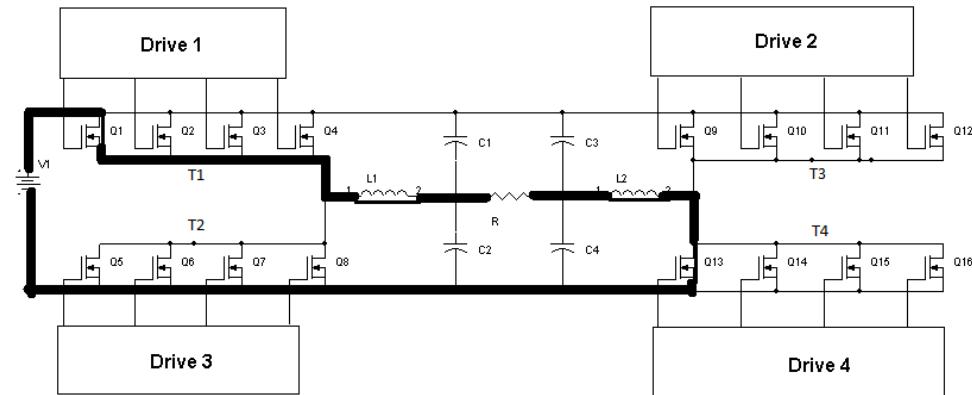

| 3.2  | Acionamento das chaves do inversor com multiplexação - etapa 1. . . . .       | 25 |

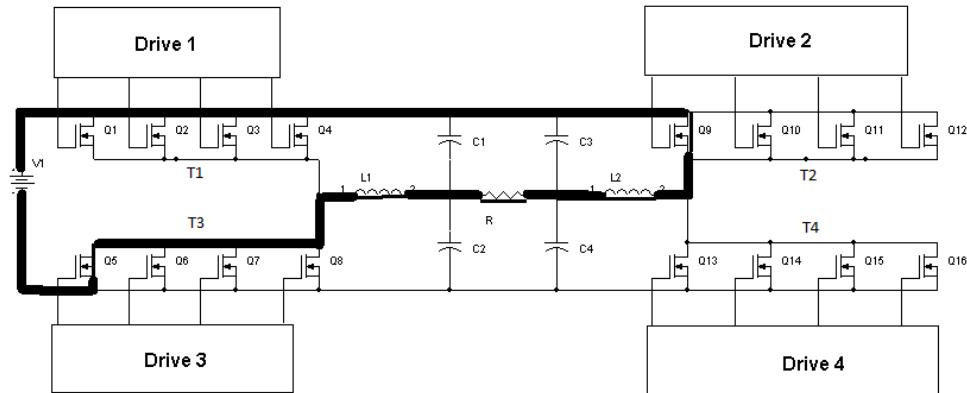

| 3.3  | Acionamento das chaves do inversor com multiplexação - etapa 2. . . . .       | 25 |

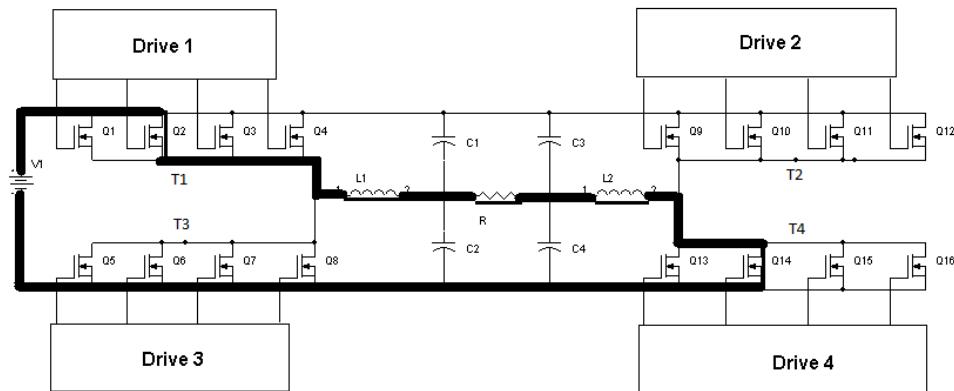

| 3.4  | Acionamento das chaves do inversor com multiplexação - etapa 3. . . . .       | 26 |

| 3.5  | Acionamento das chaves do inversor com multiplexação - etapa 4. . . . .       | 26 |

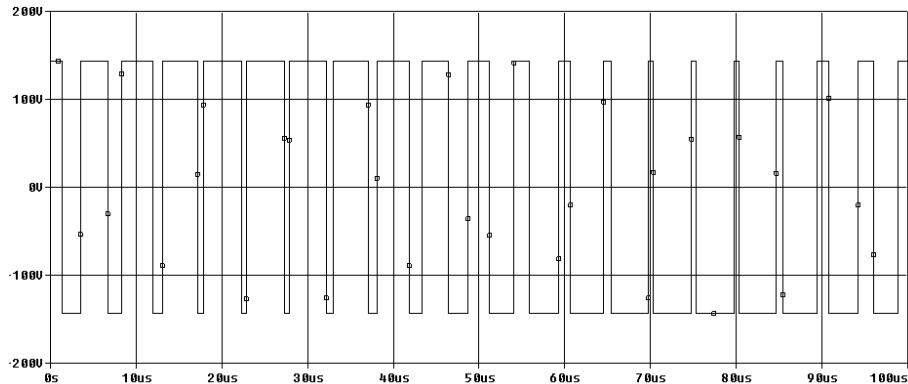

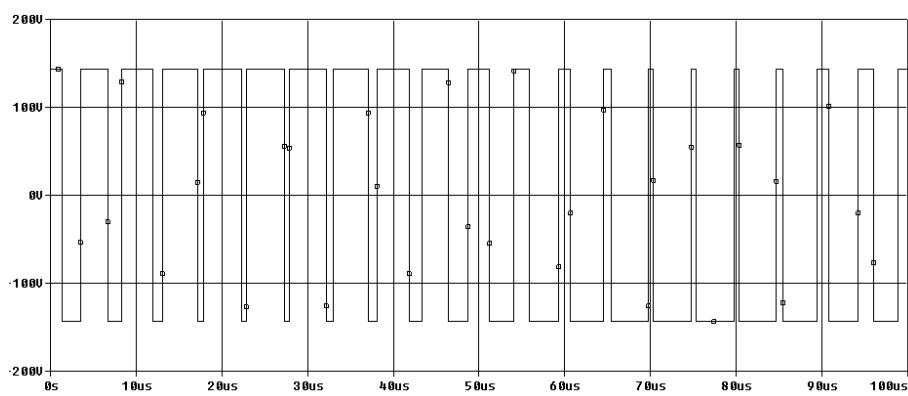

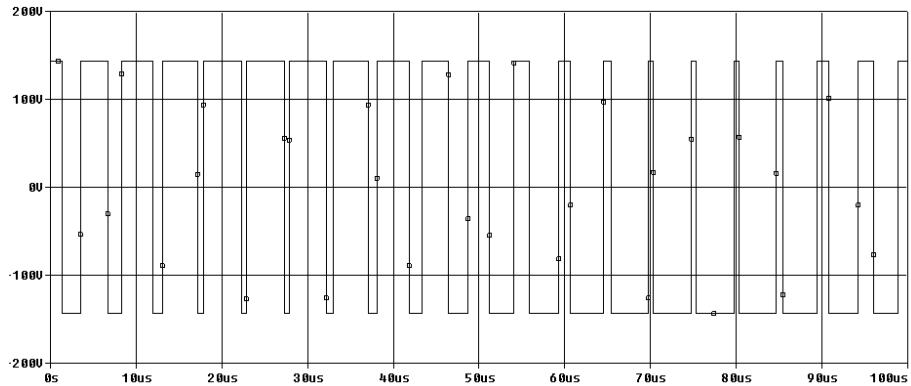

| 3.6  | Sinal PWM amplificado na carga do inversor. . . . .                           | 27 |

| 3.7  | Sinal PWM em um dos braços do inversor. . . . .                               | 27 |

| 3.8  | Sinal <i>PWM</i> complementar ao primeiro braço do inversor. . . . .          | 28 |

|      |                                                                                                                        |    |

|------|------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | Geração do sinal PWM pela comparação de uma onda triangular com um sinal senoidal.                                     | 28 |

| 3.10 | Oscilações presentes no chaveamento de MOSFETs, oriundas das interações entre capacitâncias e indutâncias do circuito. | 29 |

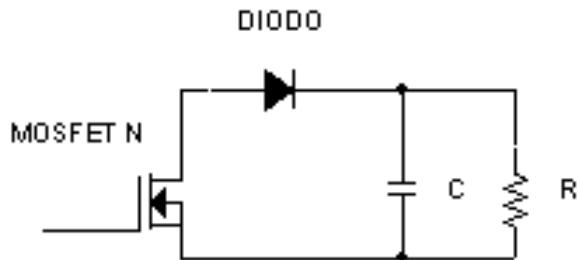

| 3.11 | Circuito de <i>snnuber</i> .                                                                                           | 29 |

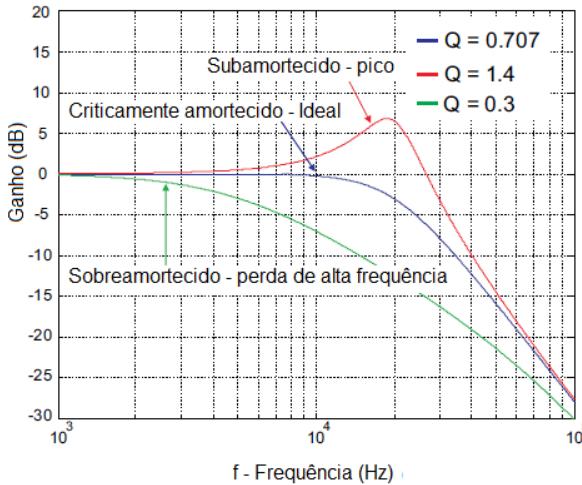

| 3.12 | Efeito do fator Q na resposta em frequência do filtro, adaptação.                                                      | 31 |

| 3.13 | Esquema do circuito de controle proposto.                                                                              | 32 |

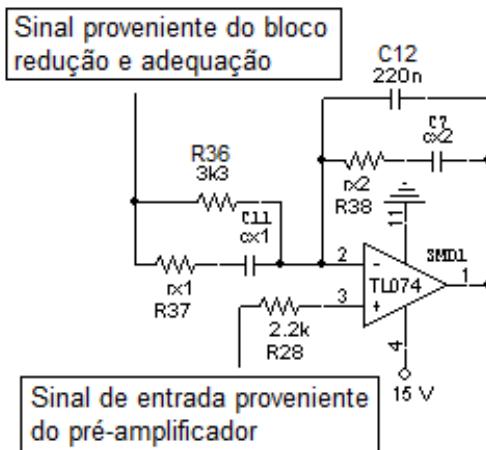

| 3.14 | Compensador utilizado para controle do inversor.                                                                       | 33 |

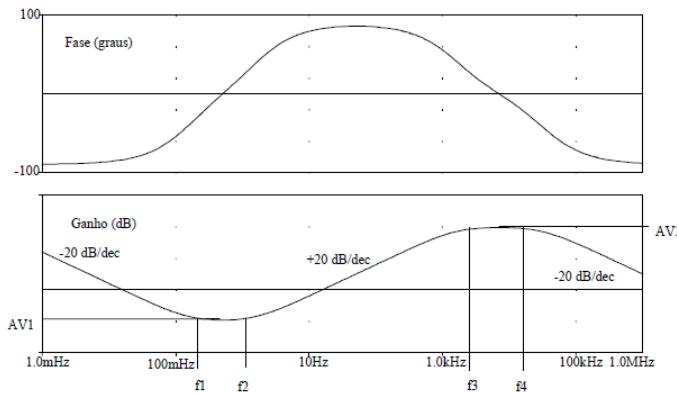

| 3.15 | Resposta em frequência e diagrama de fase para o compensador analisado.                                                | 34 |

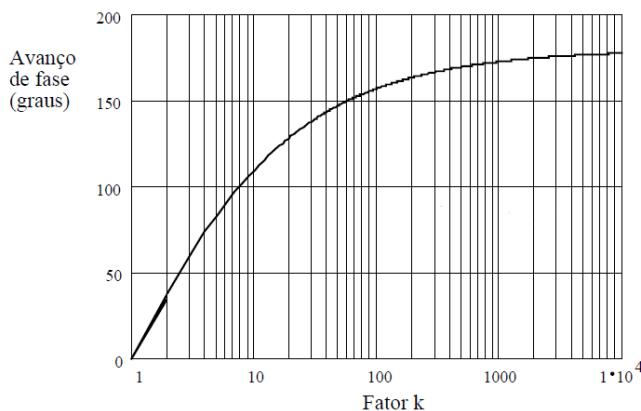

| 3.16 | Avanço de fase em função do fator <i>k</i> , adaptação.                                                                | 34 |

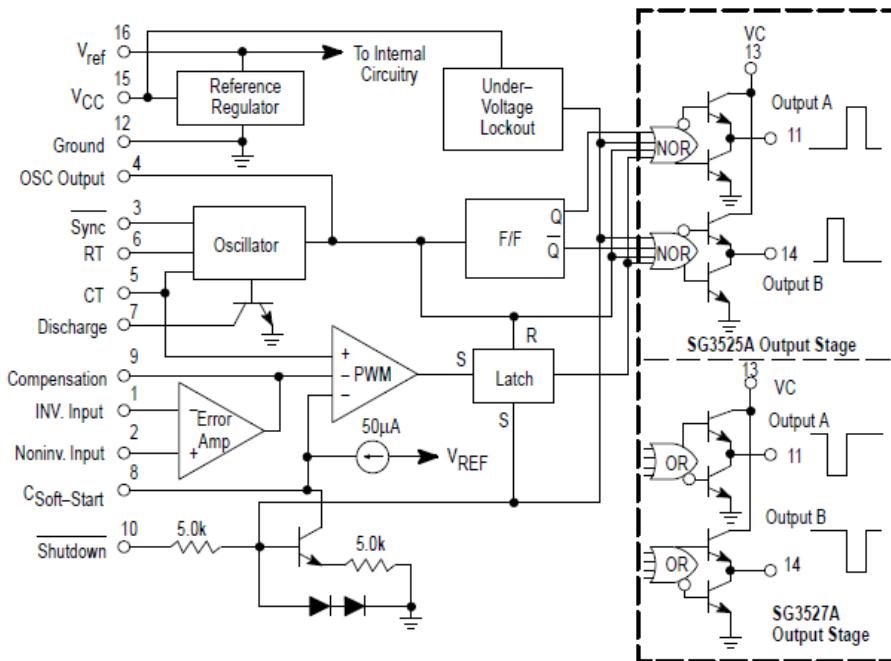

| 3.17 | Circuito interno do SG 3525, disponível em seu <i>datasheet</i> .                                                      | 36 |

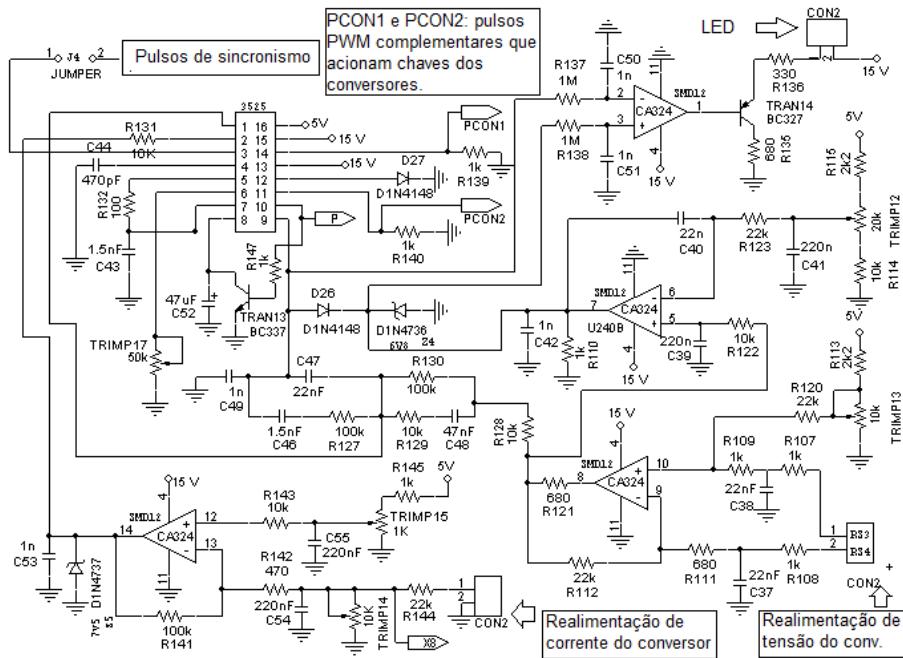

| 3.18 | Circuito de controle implementado para controle dos conversores DC/DC.                                                 | 37 |

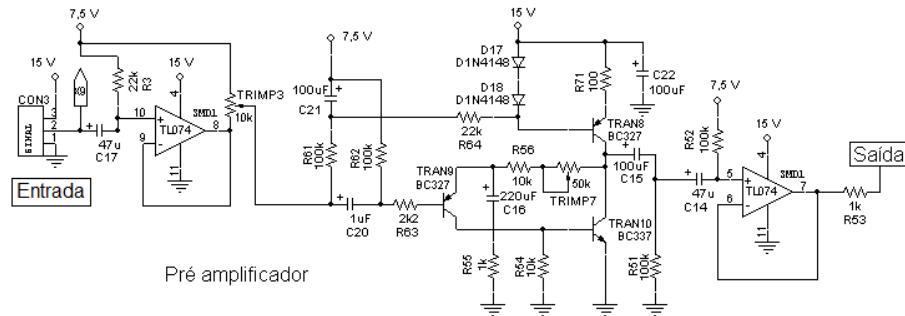

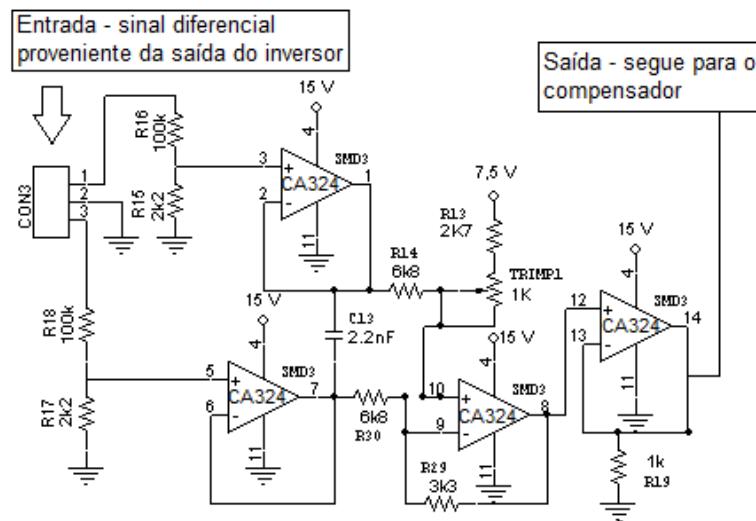

| 3.19 | Circuito implementado para o pré-amplificador de áudio.                                                                | 38 |

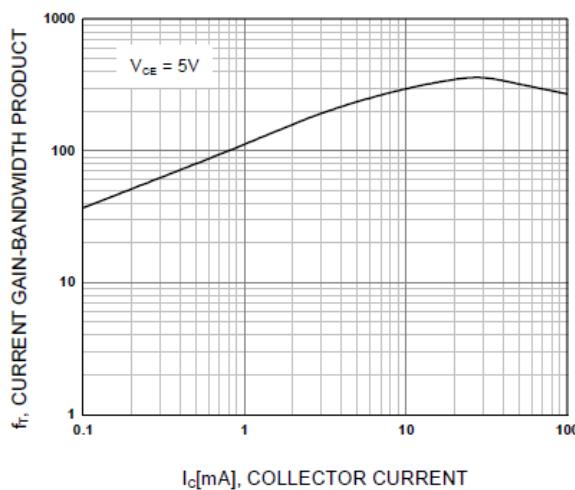

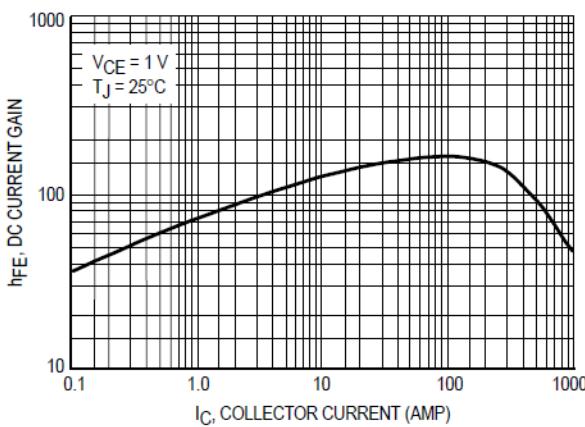

| 3.20 | Curva de ganho para o transistor BC549, extraída de seu <i>datasheet</i> .                                             | 39 |

| 3.21 | Curva de ganho para o transistor BC337, extraída de seu <i>datasheet</i> .                                             | 39 |

| 3.22 | Esquemático do circuito para redução e adequação do sinal de saída do inversor.                                        | 40 |

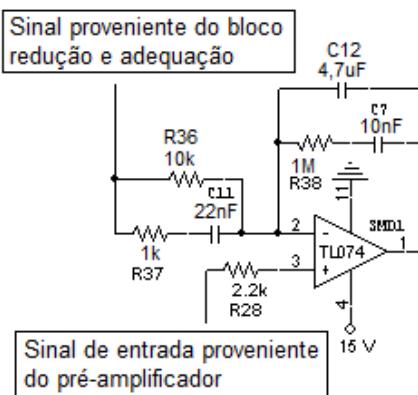

| 3.23 | Filtro e limitador do sinal proporcional ao erro na saída do inversor.                                                 | 41 |

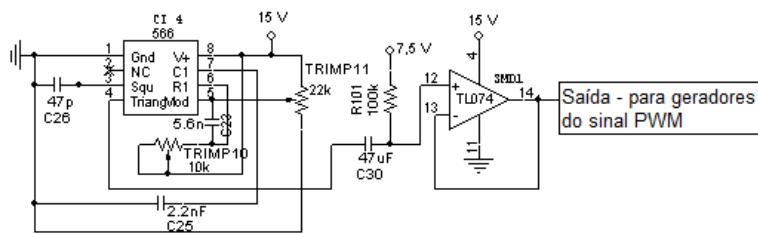

| 3.24 | Gerador de onda triangular e quadrada para pulsos PWM e sincronismo.                                                   | 42 |

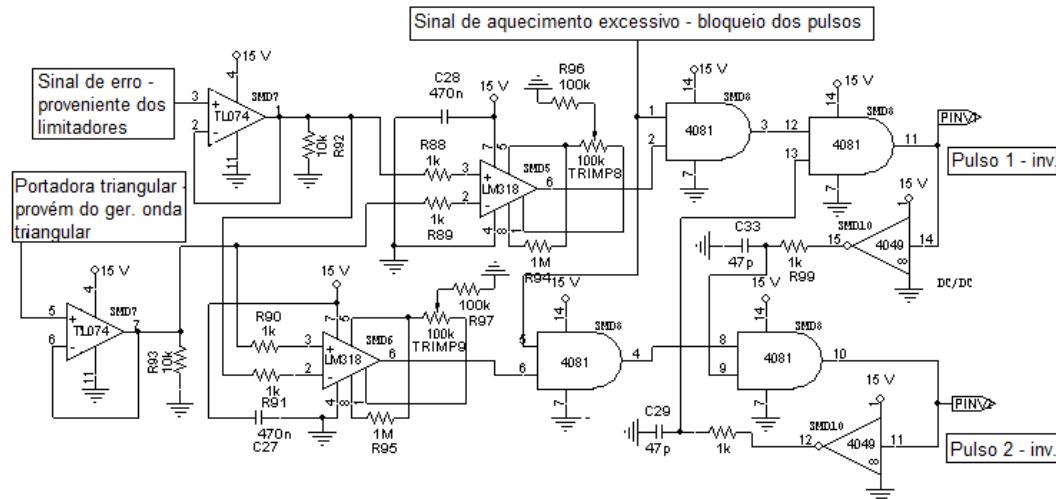

| 3.25 | Comparadores para a geração dos pulsos PWM.                                                                            | 43 |

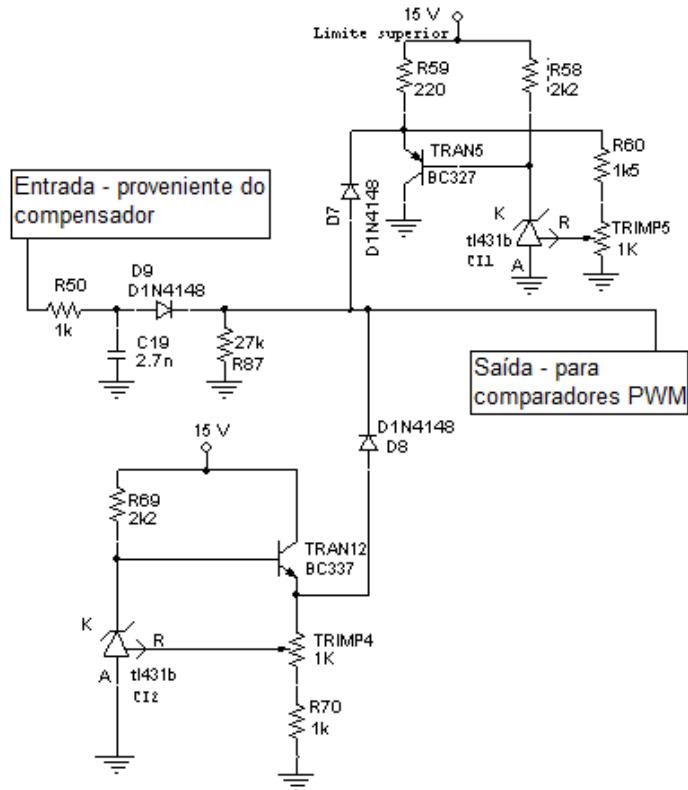

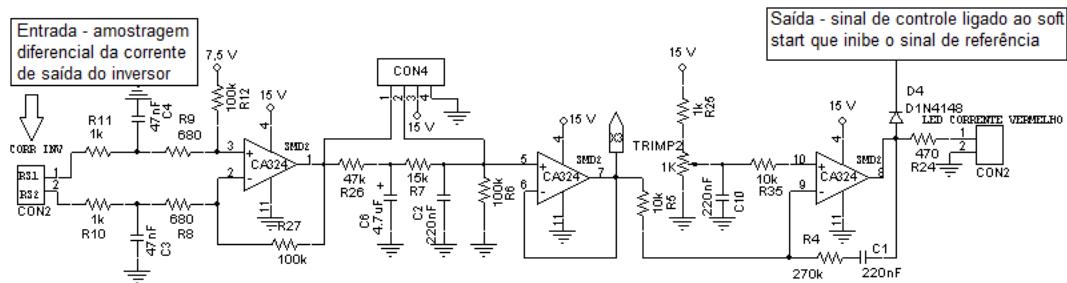

| 3.26 | Circuito de controle de corrente do inversor.                                                                          | 44 |

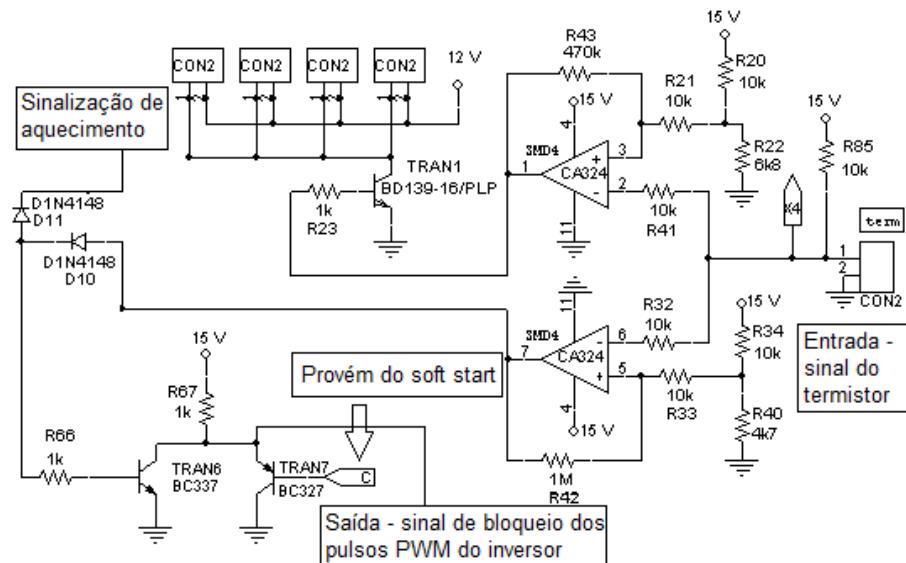

| 3.27 | Circuito de controle para detecção de aquecimento excessivo.                                                           | 45 |

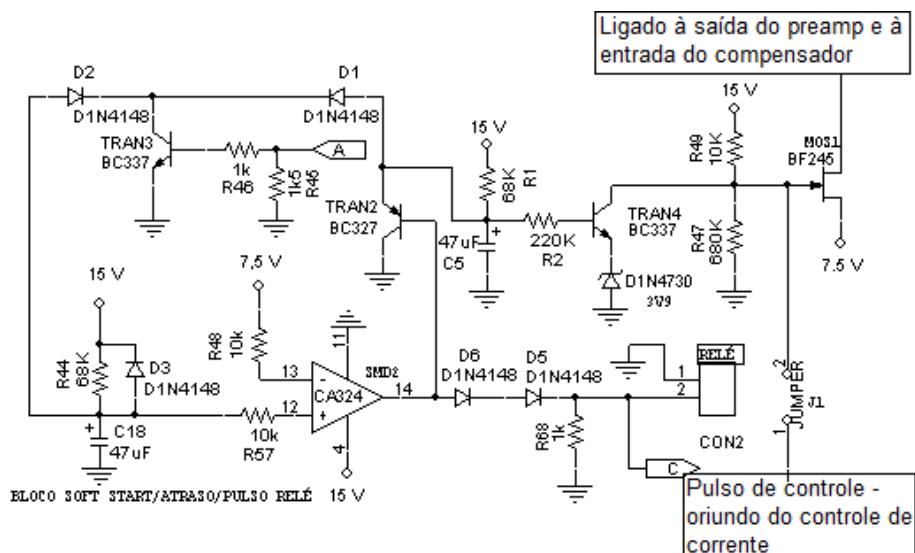

| 3.28 | Circuito de <i>soft start</i> .                                                                                        | 46 |

| 3.29 | Circuito de sincronismo.                                                                                               | 48 |

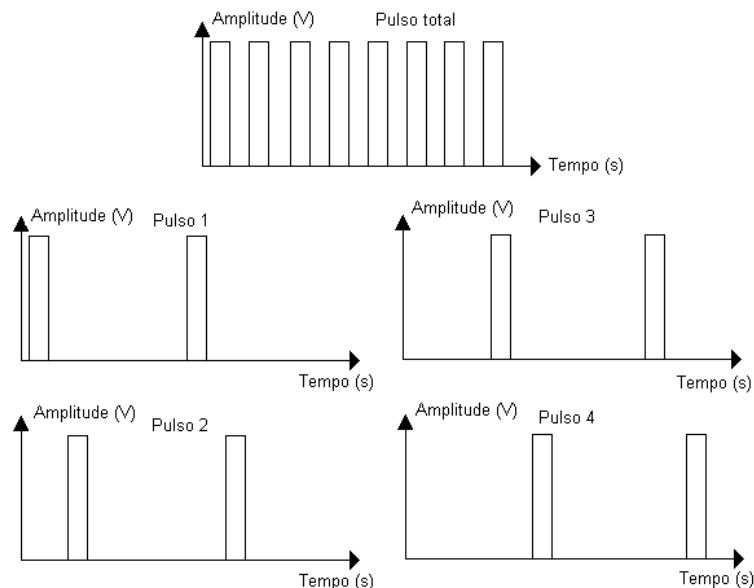

| 3.30 | Exemplo de multiplexação de um pulso quadrado.                                                                         | 49 |

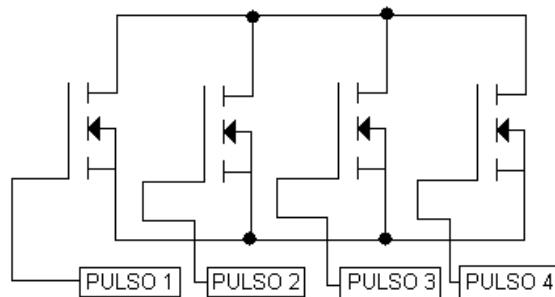

| 3.31 | Exemplo de grupo de transistores acionados por pulsos multiplexados.                                                   | 50 |

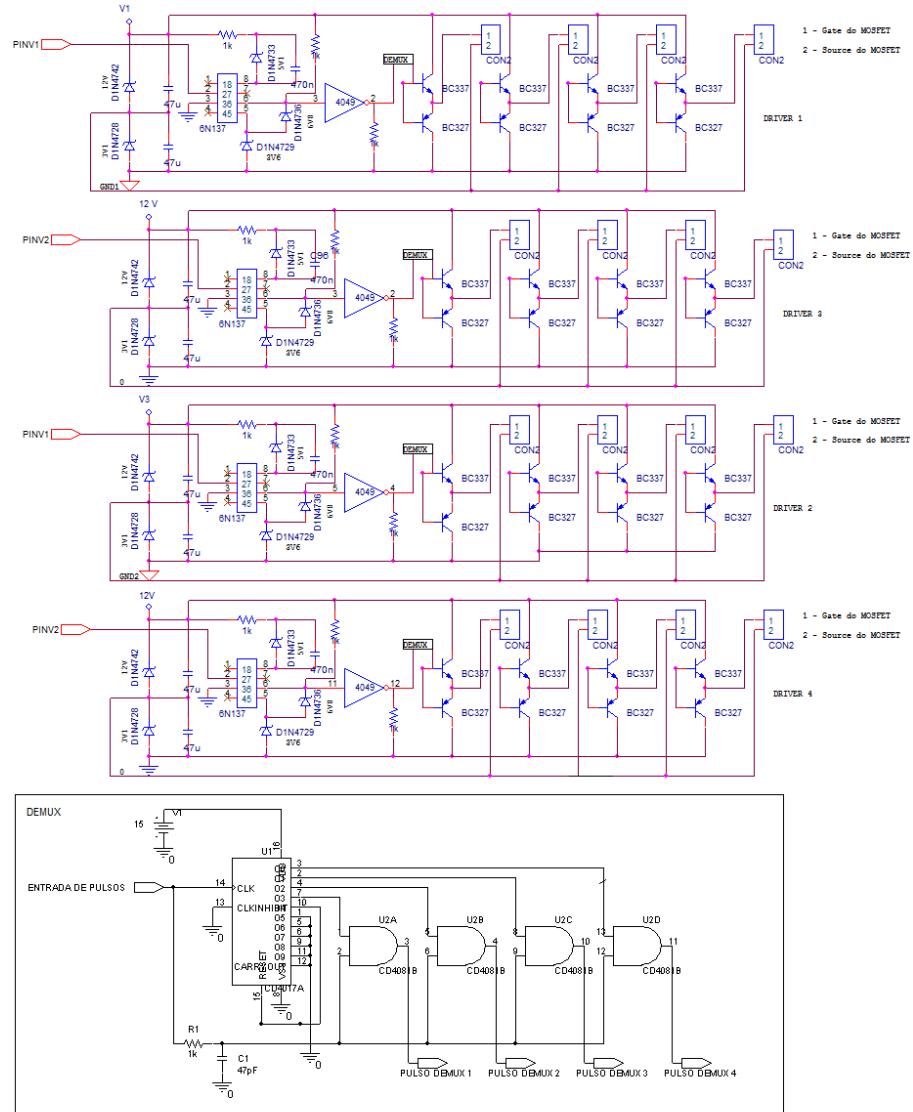

| 3.32 | Esquemático do circuito de <i>driver</i> implementado.                                                                 | 51 |

| 3.33 | Aspecto da tensão negativa gerada pelo circuito de drive (a) e transitórios no acionamento das chaves (b).             | 51 |

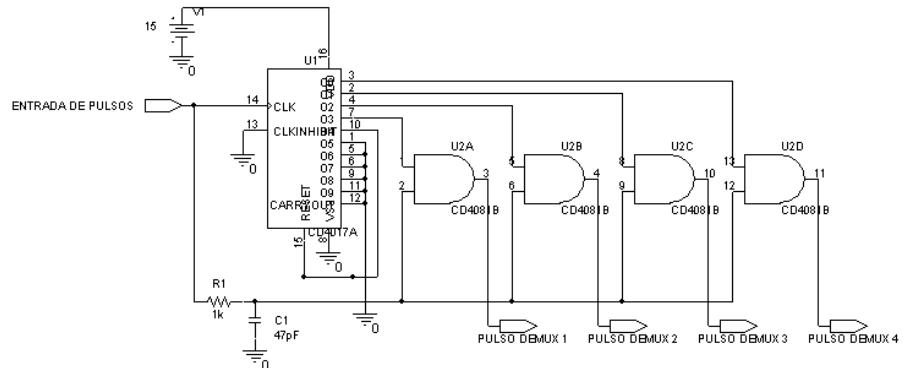

| 3.34 | Multiplexador de pulsos.                                                                                               | 52 |

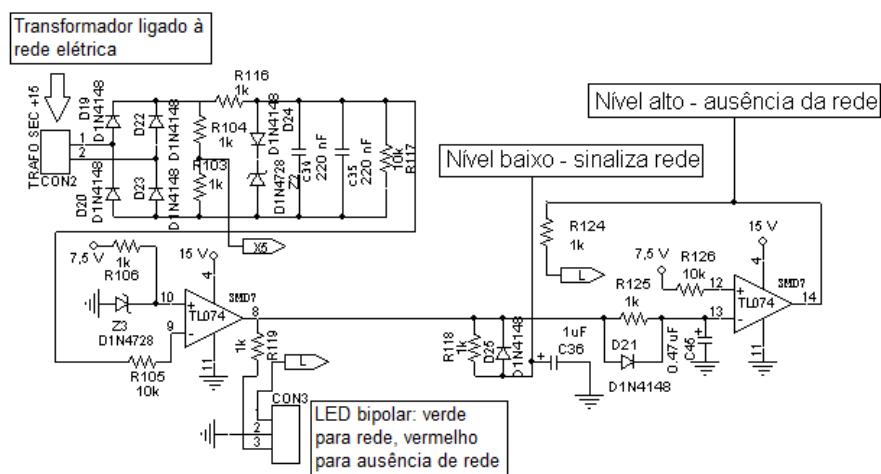

| 3.35 | Detector e sinalizador da presença do sinal da rede elétrica na alimentação dos conversores.                           | 53 |

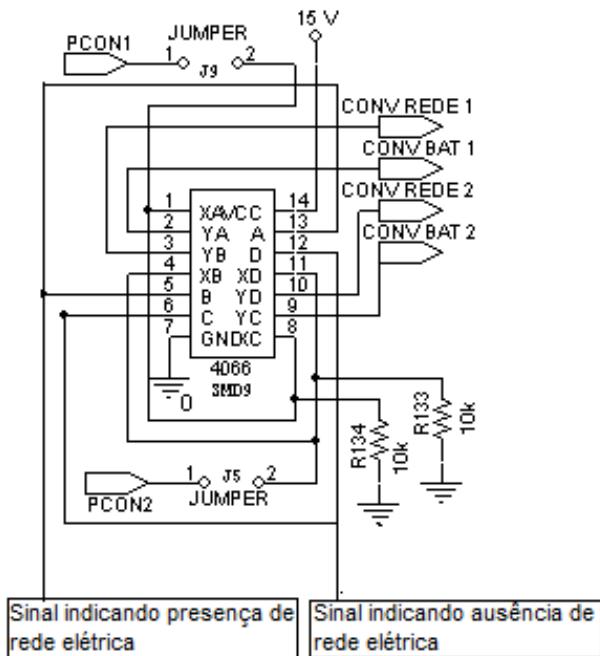

| 3.36 | Comutador utilizado para acionar os conversores.                                                                       | 55 |

|                                                                                                                                            |    |

|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.37 Circuito de monitoramento das baterias. . . . .                                                                                       | 56 |

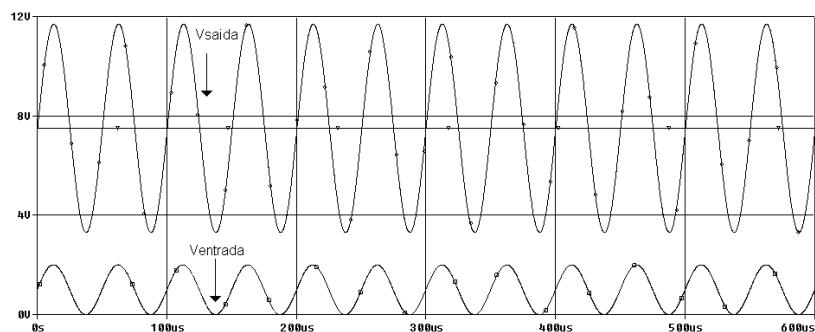

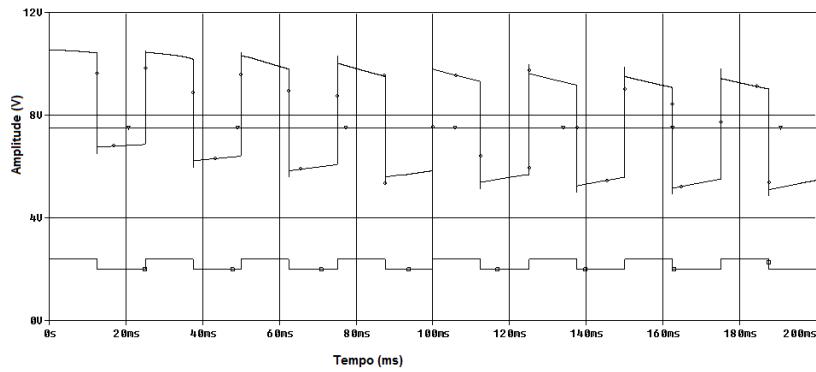

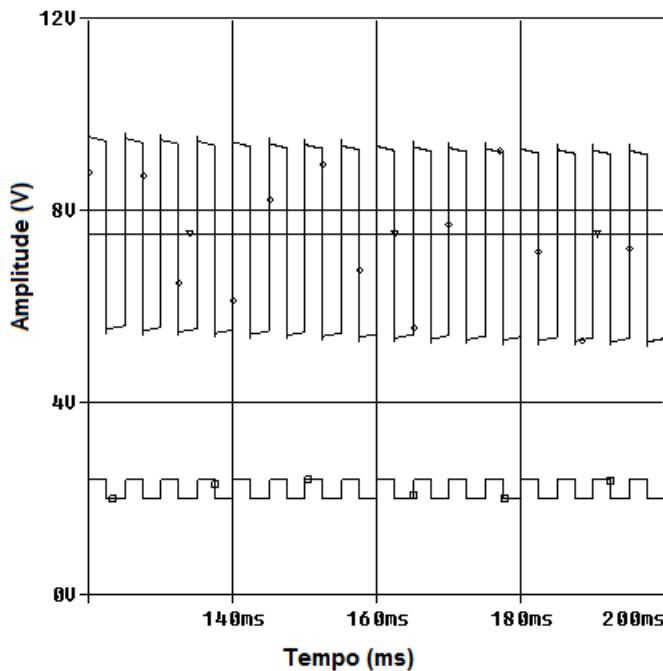

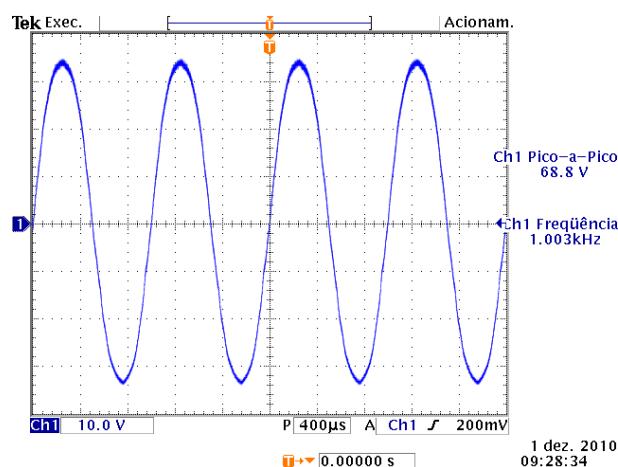

| 4.1 Tensão de entrada e saída do pré-amplificador para frequência de 1 kHz. . . . .                                                        | 60 |

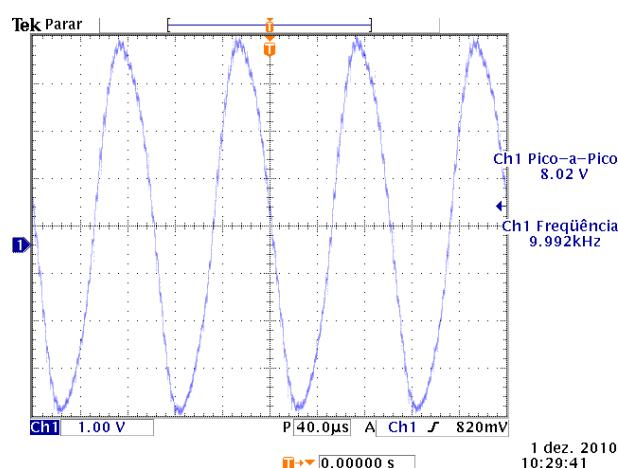

| 4.2 Tensão de entrada e saída do pré-amplificador para frequência de 1 kHz, com ganho elevado. . . . .                                     | 60 |

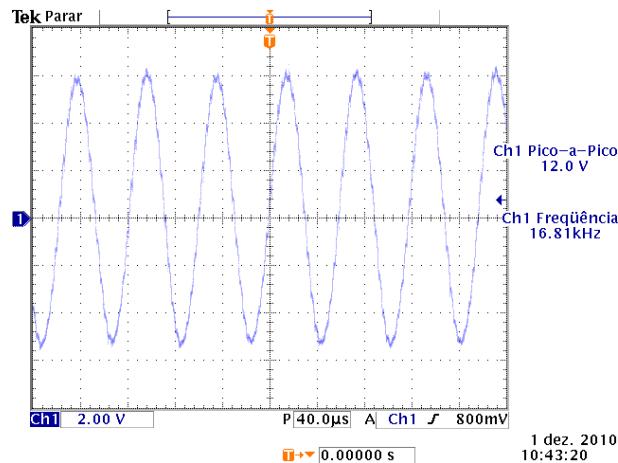

| 4.3 Tensão de entrada e saída do pré-amplificador para frequência de 30 Hz. . . . .                                                        | 61 |

| 4.4 Tensão de entrada e saída do pré-amplificador para frequência de 20 kHz. . . . .                                                       | 61 |

| 4.5 Tensão de entrada e saída do pré-amplificador para frequência de 20 kHz e ganho elevado. . . . .                                       | 62 |

| 4.6 Tensão de entrada e saída do pré-amplificador para frequência de 20kHz e onda quadrada. . . . .                                        | 62 |

| 4.7 Tensão de entrada e saída do pré-amplificador para frequência de 40Hz e onda quadrada. . . . .                                         | 63 |

| 4.8 Tensão de entrada e saída do pré-amplificador para frequência de 40 Hz e onda quadrada, utilizando transistores BC549 e BC559. . . . . | 63 |

| 4.9 Tensão de entrada e saída do pré-amplificador para frequência de 200 Hz e onda quadrada. . . . .                                       | 64 |

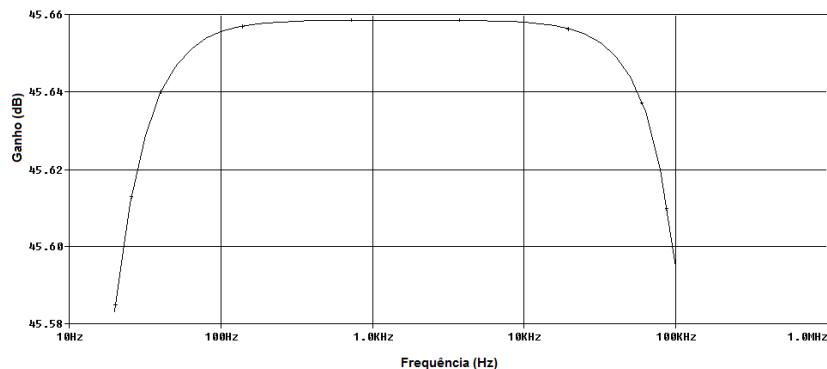

| 4.10 Curva de ganho do pré-amplificador, em dB, para frequências de 20 Hz a 100 kHz. .                                                     | 64 |

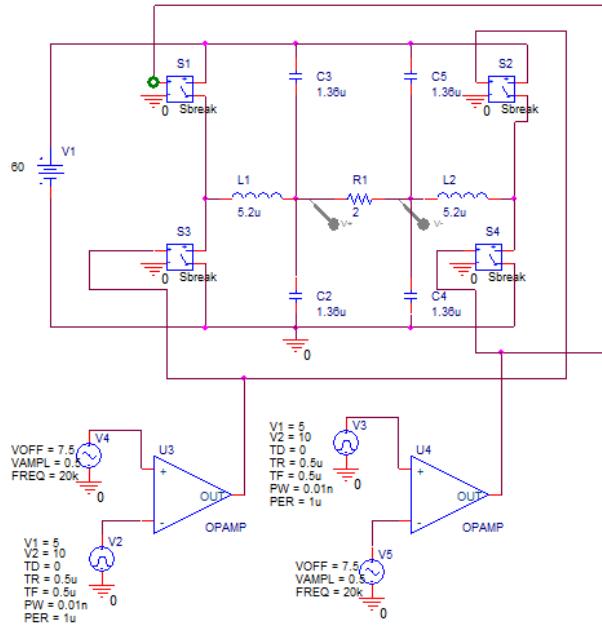

| 4.11 Circuito para simulação do ivnerson proposto no trabalho, com respectivo filtro de saída. .                                           | 65 |

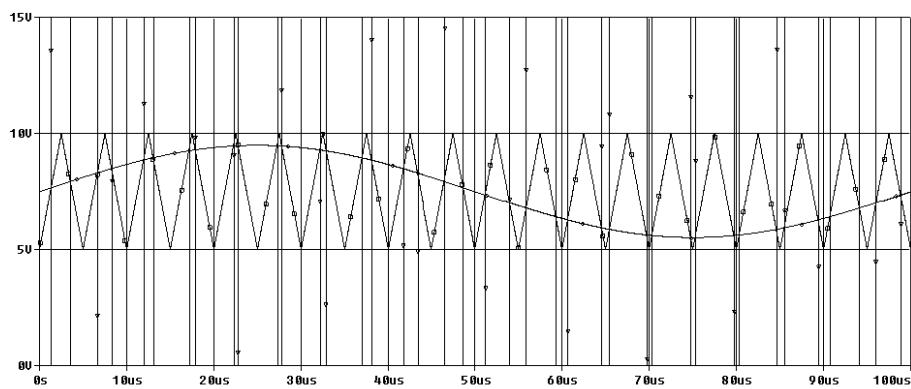

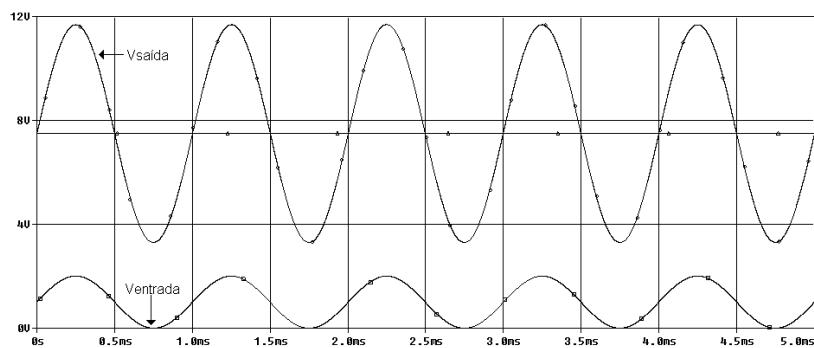

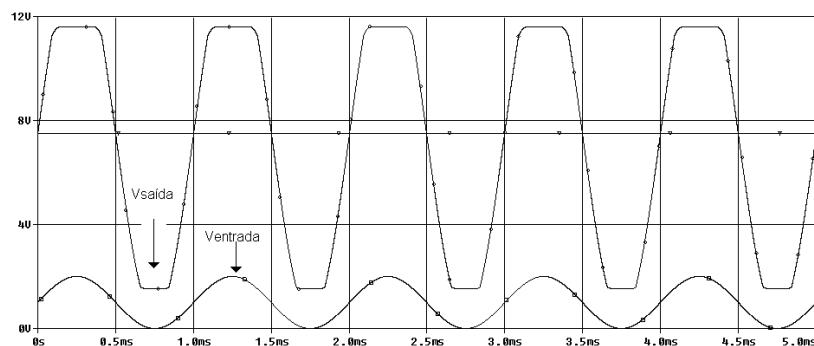

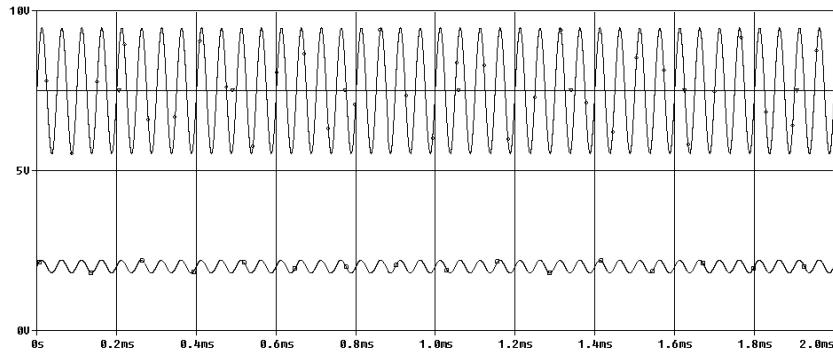

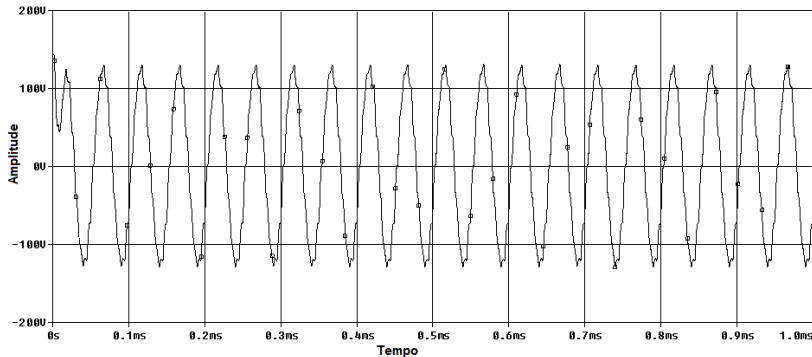

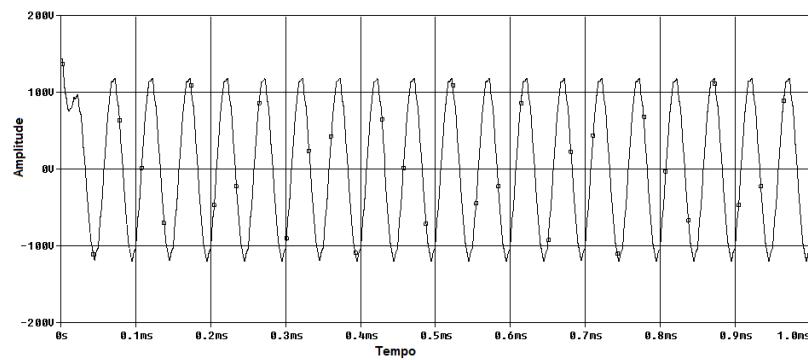

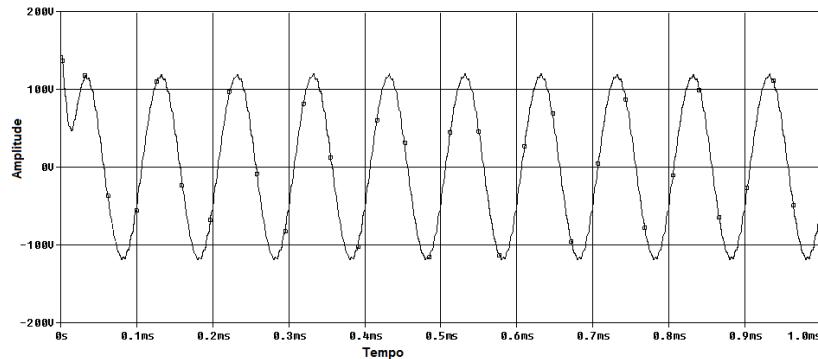

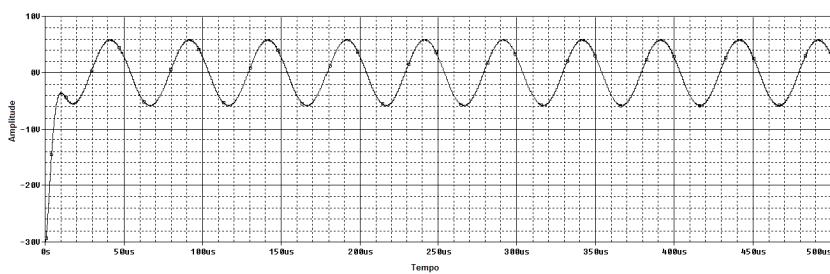

| 4.12 Tensão de saída no inversor para entrada senoidal de 20 kHz. . . . .                                                                  | 65 |

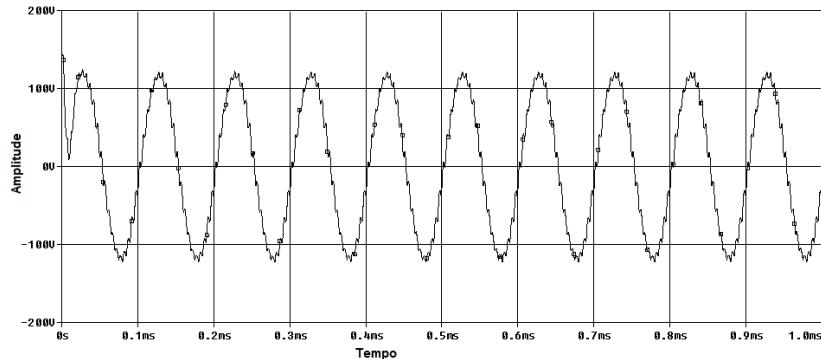

| 4.13 Tensão de saída no inversor para entrada senoidal de 10 kHz. . . . .                                                                  | 66 |

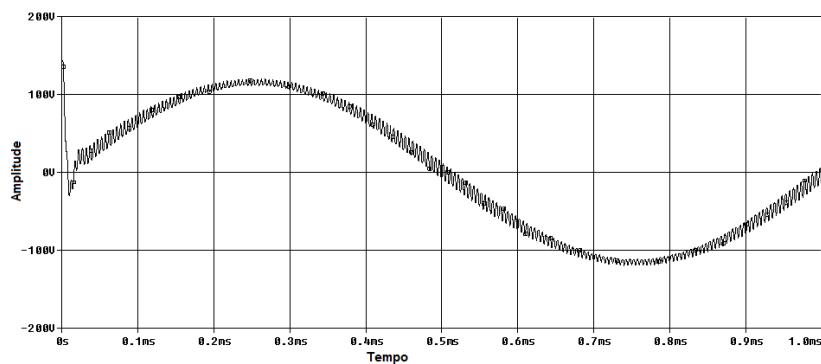

| 4.14 Tensão de saída no inversor para entrada senoidal de 1 kHz. . . . .                                                                   | 66 |

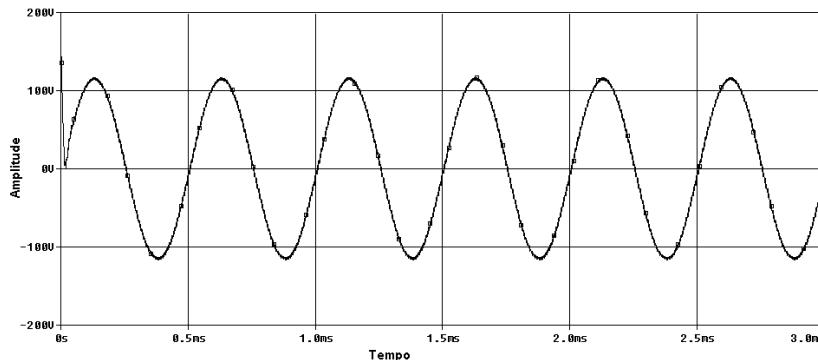

| 4.15 Tensão de saída no inversor para entrada senoidal de 20 kHz, com capacitor em paralelo com a carga. . . . .                           | 66 |

| 4.16 Tensão de saída no inversor para entrada senoidal de 10 kHz, com capacitor em paralelo com a carga. . . . .                           | 67 |

| 4.17 Tensão de saída no inversor para entrada senoidal de 2 kHz, com capacitor em paralelo com a carga. . . . .                            | 67 |

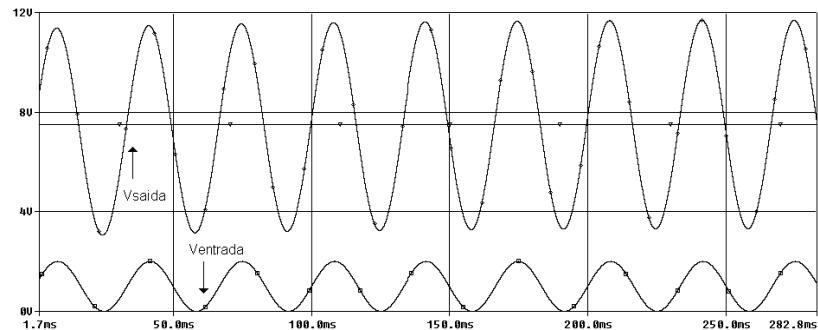

| 4.18 Tensão de saída no inversor para entrada senoidal de 20 kHz, com portadora triangular a 333 kHz. . . . .                              | 68 |

| 4.19 Tensão de saída no inversor para entrada senoidal de 20 kHz, com portadora triangular a 1 MHz. . . . .                                | 68 |

| 4.20 Tensão de saída no inversor para entrada senoidal de 20 kHz, com portadora triangular a 1 MHz e amplitude reduzida. . . . .           | 68 |

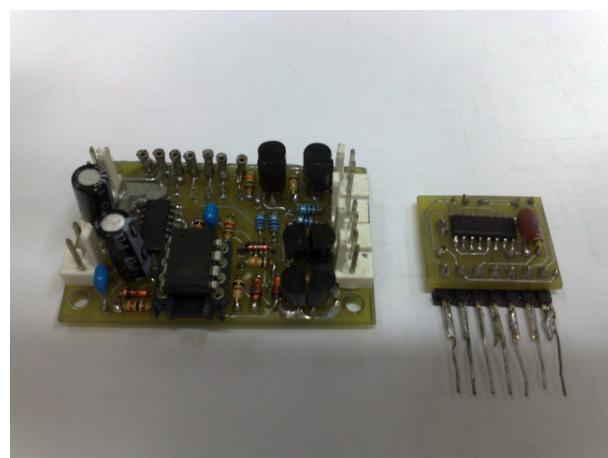

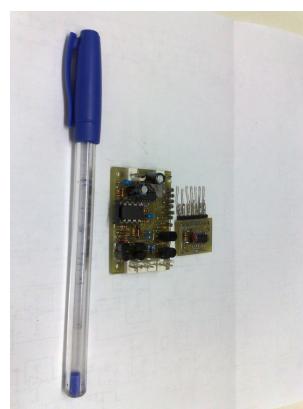

| 4.21 Circuito de <i>driver</i> e multiplexador de pulsos implementados. . . . .                                                            | 69 |

|                                                                                                                                                                                  |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.22 Comparativo do tamanho do circuito de <i>driver</i> e multiplexador de pulsos implementados em relação a uma caneta esferográfica comum. . . . .                            | 69 |

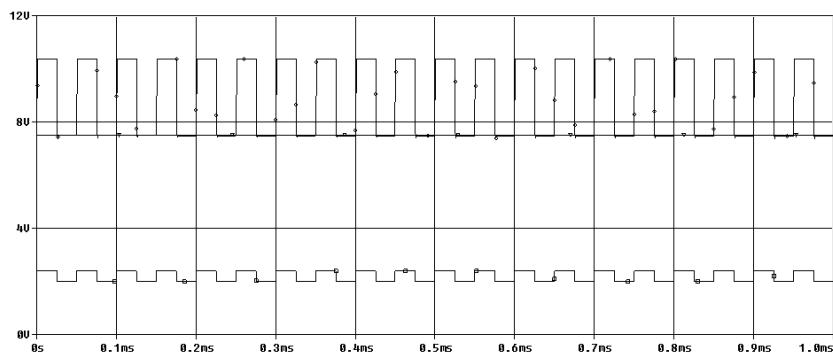

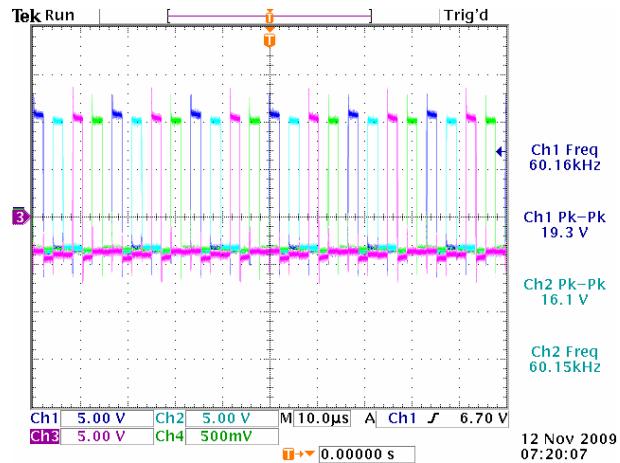

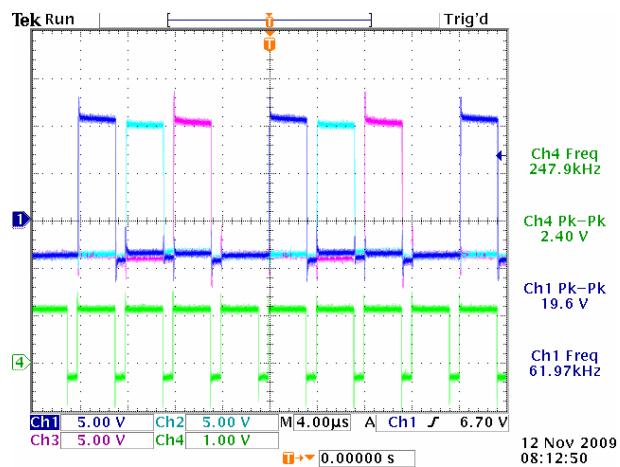

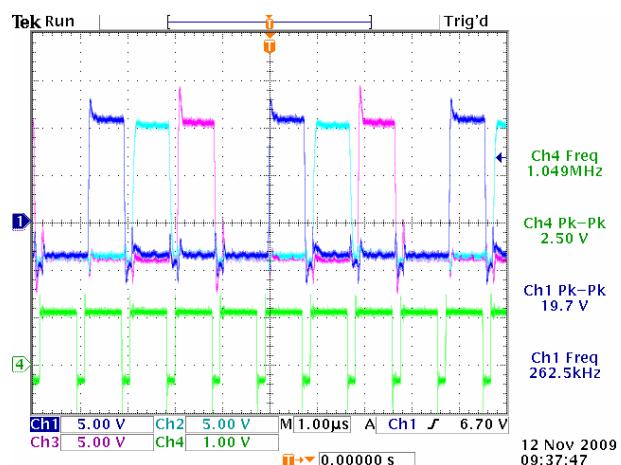

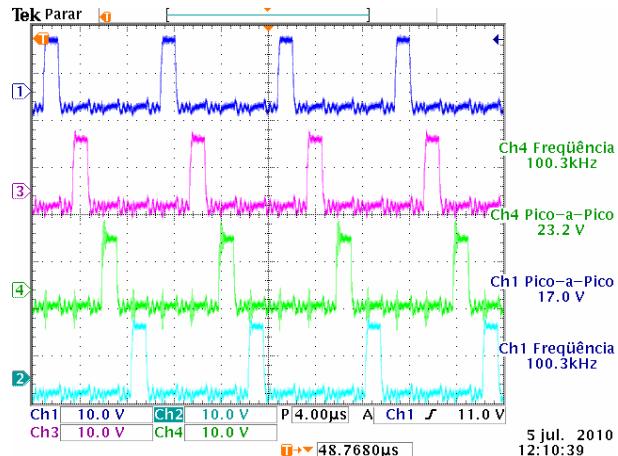

| 4.23 Pulsos na saída do circuito de <i>driver</i> para frequência de 240 kHz, com multiplexação de pulsos. . . . .                                                               | 70 |

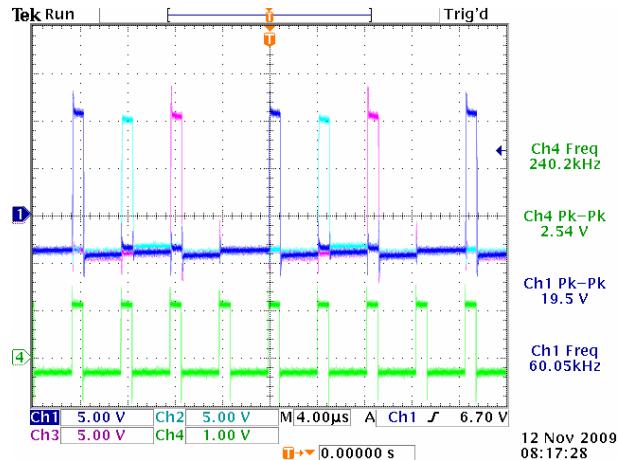

| 4.24 Comparativo dos pulsos na saída do circuito de <i>driver</i> com relação à entrada, para frequência de 240 kHz, com multiplexação de pulsos e razão cíclica máxima. . . . . | 70 |

| 4.25 Comparativo dos pulsos na saída do circuito de <i>driver</i> com relação à entrada, para frequência de 240 kHz, com multiplexação de pulsos e razão cíclica mínima. . . . . | 71 |

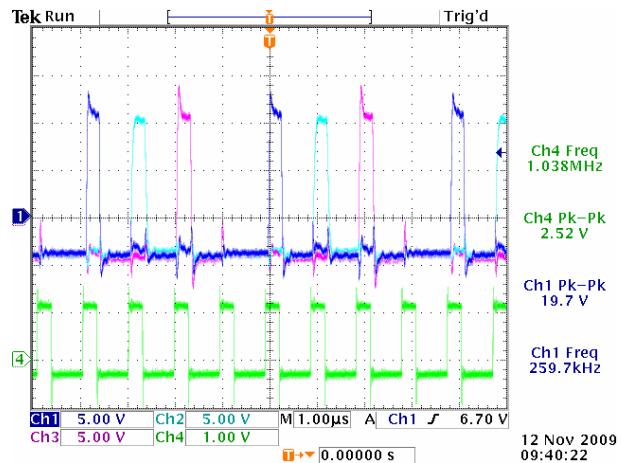

| 4.26 Pulsos na saída do circuito de <i>driver</i> , para frequência de 1 MHz, com multiplexação de pulsos. . . . .                                                               | 71 |

| 4.27 Comparativo dos pulsos na saída do circuito de <i>driver</i> com relação à entrada, para frequência de 1 MHz, com multiplexação de pulsos e razão cíclica mínima. . . . .   | 72 |

| 4.28 Comparativo dos pulsos na saída do circuito de <i>driver</i> com relação à entrada, para frequência de 1 MHz, com multiplexação de pulsos e razão cíclica máxima. . . . .   | 72 |

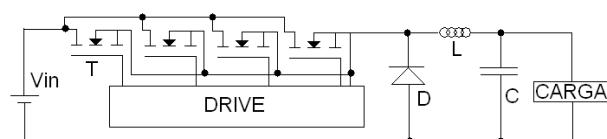

| 4.29 Esquemático do conversor <i>Buck</i> implementado para testes. . . . .                                                                                                      | 72 |

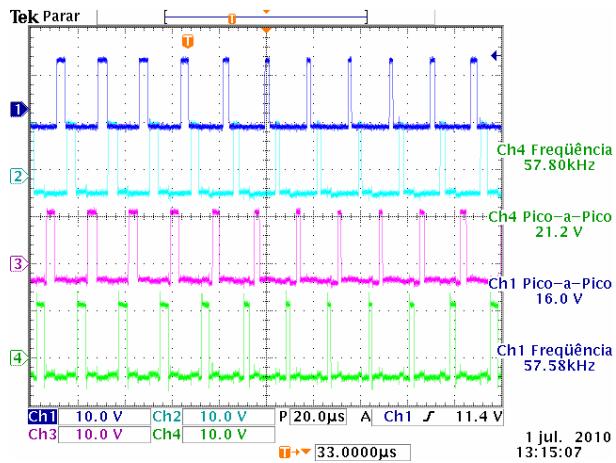

| 4.30 Pulsos nas chaves do conversor <i>Buck</i> implementado, em carga, com frequência de 200 kHz. . . . .                                                                       | 73 |

| 4.31 Pulsos nas chaves do conversor <i>Buck</i> implementado, em carga, com frequência de 200 kHz - detalhe. . . . .                                                             | 74 |

| 4.32 Pulsos nas chaves do conversor <i>Buck</i> implementado, em carga, com frequência de 400 kHz. . . . .                                                                       | 74 |

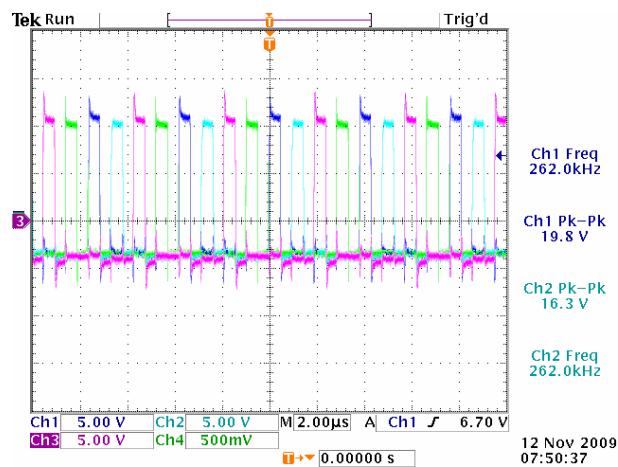

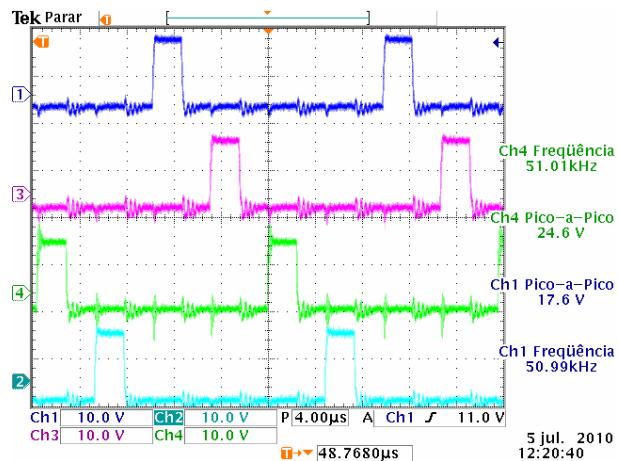

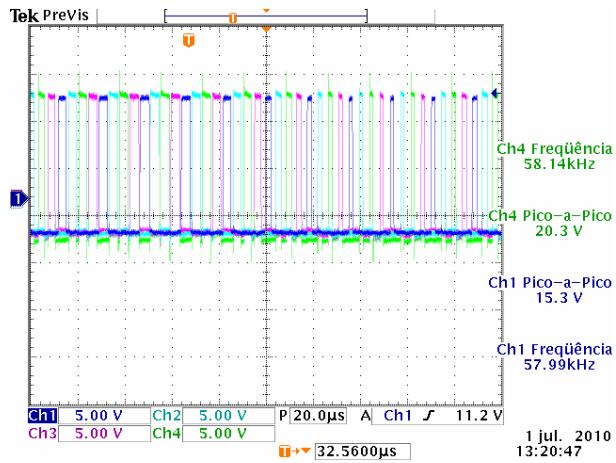

| 4.33 Multiplexação de um pulso PWM a 200 kHz. . . . .                                                                                                                            | 75 |

| 4.34 Multiplexação de um pulso PWM a 200 kHz (com sobreposição dos pulsos de saída). . . . .                                                                                     | 75 |

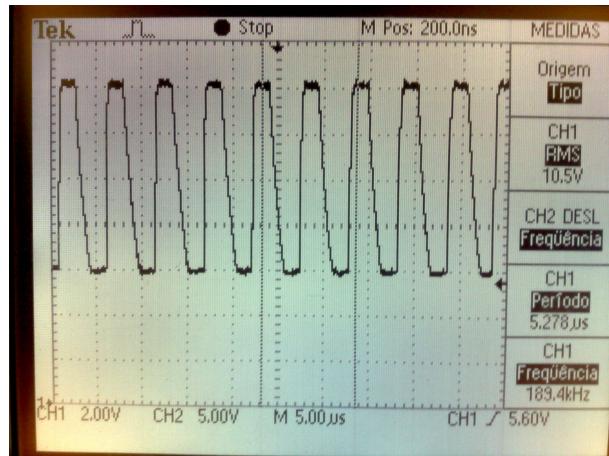

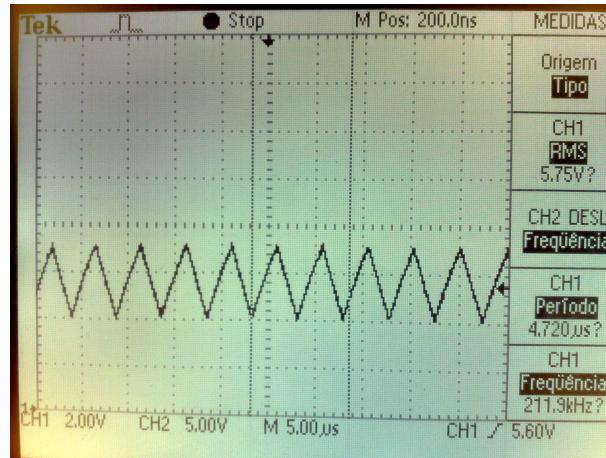

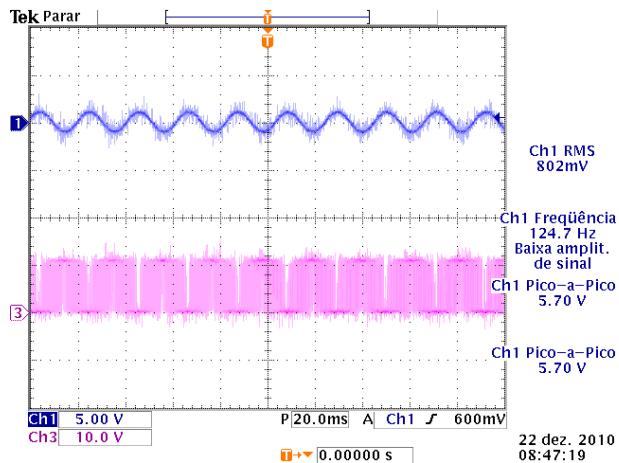

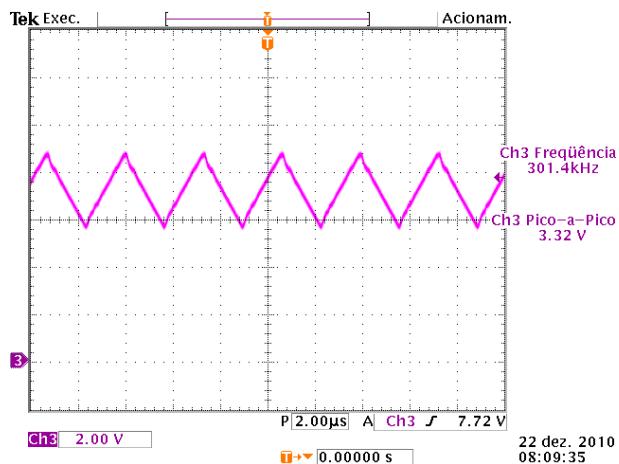

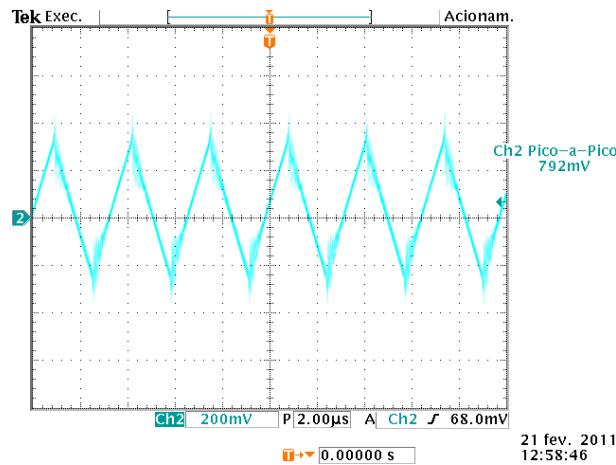

| 4.35 Aspecto da onda quadrada gerada pelo NE566, com frequência em torno de 200 kHz. . . . .                                                                                     | 76 |

| 4.36 Aspecto da onda triangular gerada pelo NE566, com frequência em torno de 200 kHz. . . . .                                                                                   | 77 |

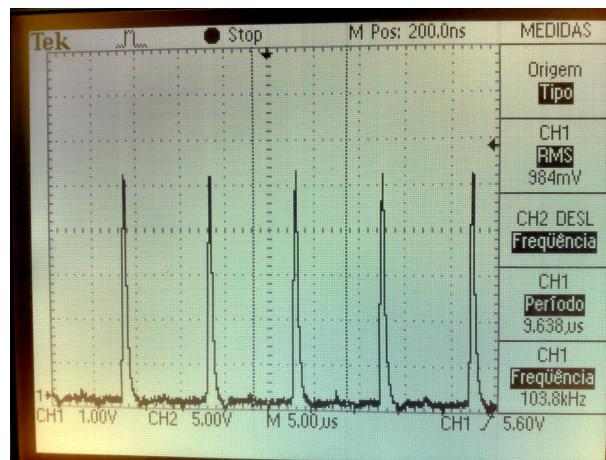

| 4.37 Aspecto dos pulsos de sincronismo gerados . . . . .                                                                                                                         | 77 |

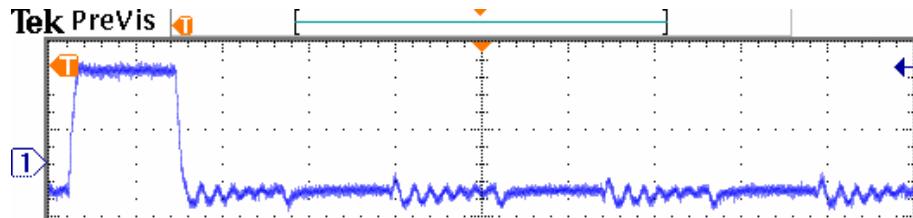

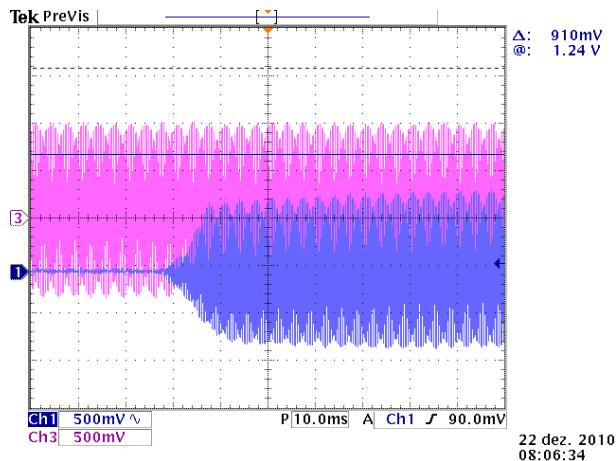

| 4.38 <i>Soft-start</i> do circuito atuando em seu acionamento. . . . .                                                                                                           | 79 |

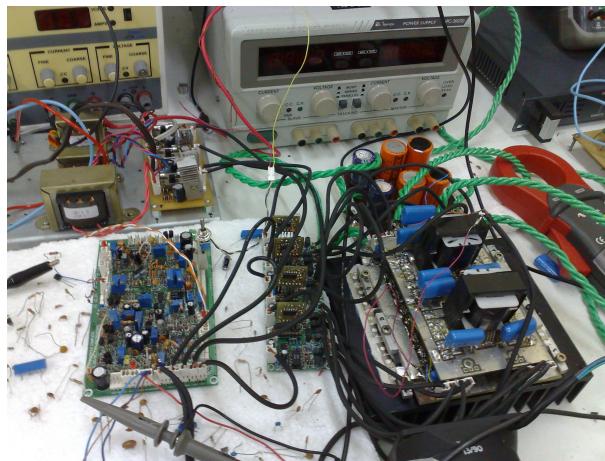

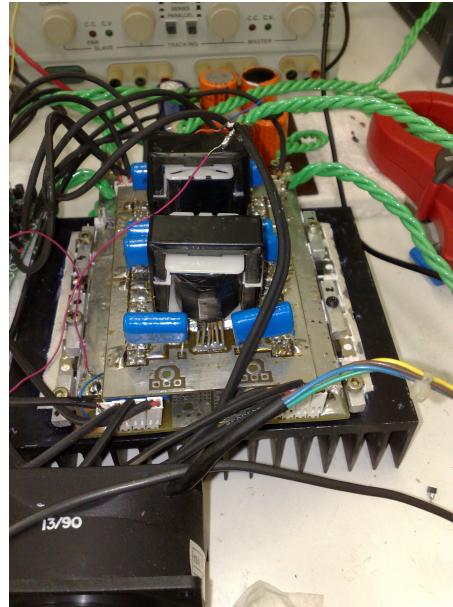

| 4.39 Foto do protótipo completo, em bancada. . . . .                                                                                                                             | 79 |

| 4.40 Foto do protótipo inversor e o respetivo filtro de saída. . . . .                                                                                                           | 80 |

| 4.41 Foto das fontes utilizadas para alimentação dos circuitos de <i>driver</i> e controle. . . . .                                                                              | 80 |

| 4.42 Foto do circuito de controle. . . . .                                                                                                                                       | 81 |

| 4.43 Esquema das diferentes referências dos circuitos de <i>driver</i> . . . . .                                                                                                 | 81 |

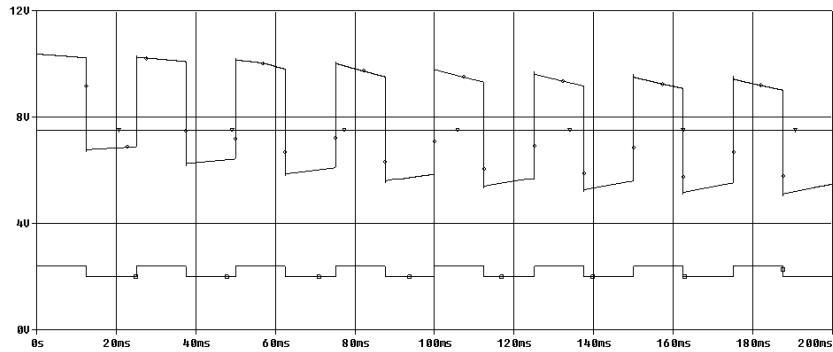

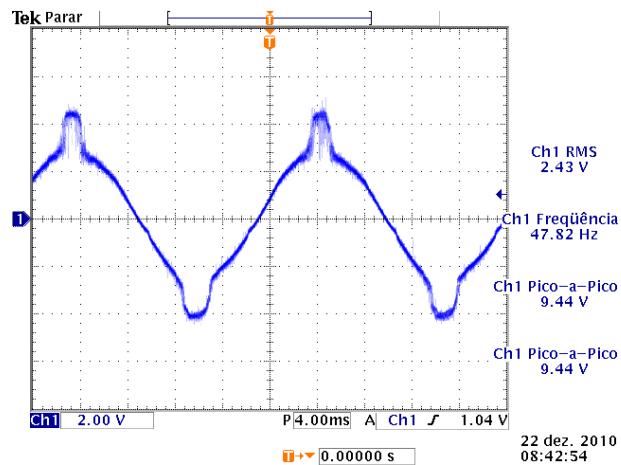

| 4.44 Forma de onda na carga, com distorção causada por erro no chaveamento. . . . .                                                                                              | 81 |

| 4.45 Aspecto dos erros na geração do pulso PWM e sinal senoidal de referência. . . . .                                                                                           | 82 |

|                                                                                                                                               |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.46 Sinal triangular de referência para geração dos pulsos PWM. . . . .                                                                      | 82 |

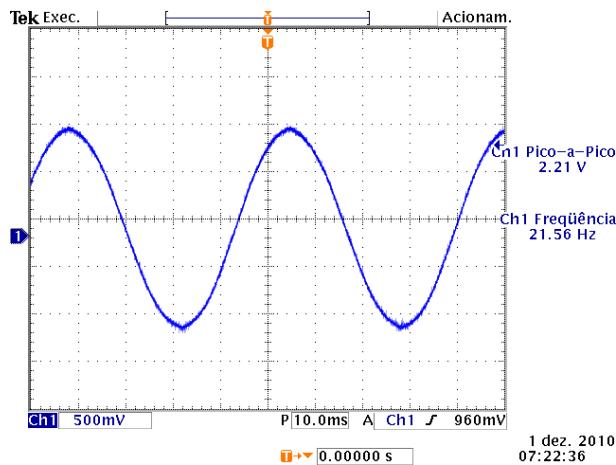

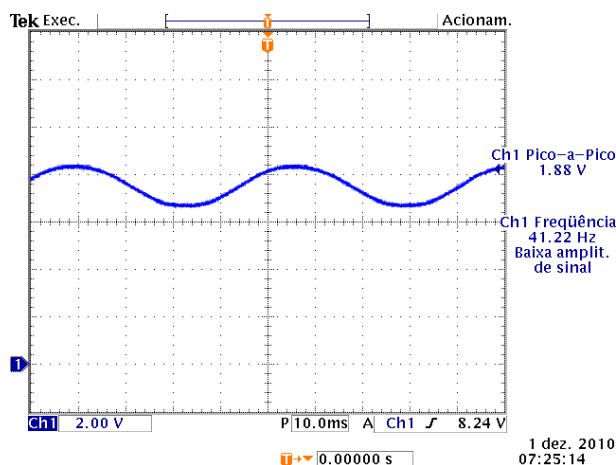

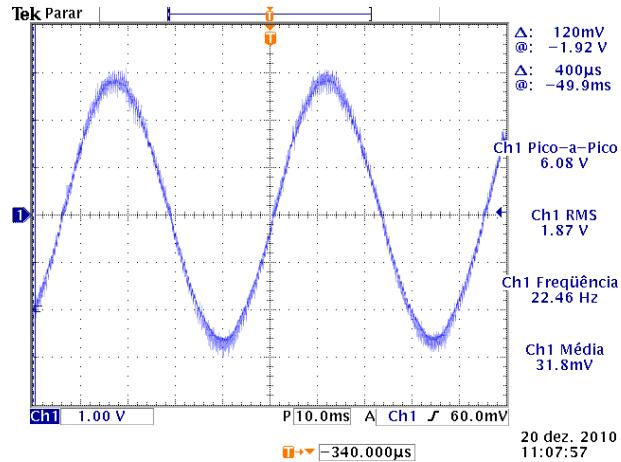

| 4.47 Sinal senoidal de referência a 20 Hz para testes em malha aberta. . . . .                                                                | 83 |

| 4.48 Sinal senoidal de referência a 20 Hz para testes em malha aberta, após passar por estágio pré-amplificador para ajuste de nível. . . . . | 83 |

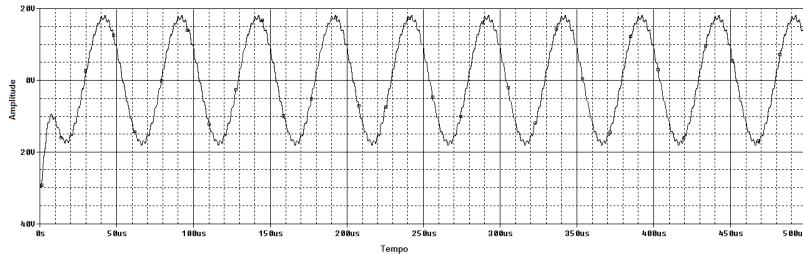

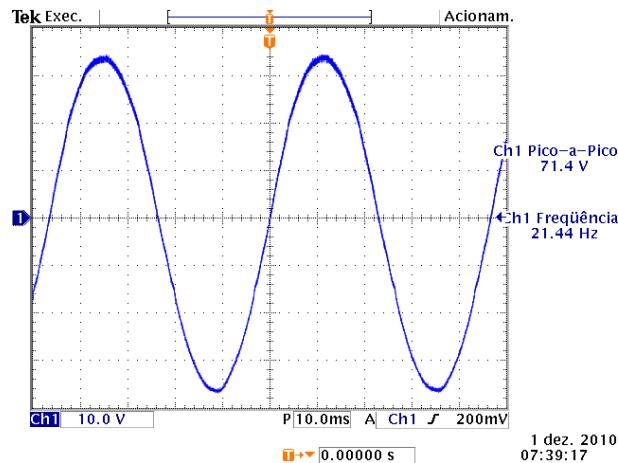

| 4.49 Sinal senoidal de saída a 20 Hz - malha aberta. . . . .                                                                                  | 84 |

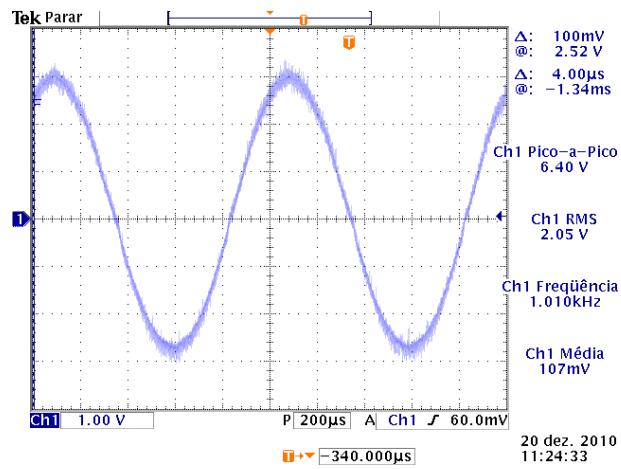

| 4.50 Sinal senoidal de saída a 1 kHz - malha aberta. . . . .                                                                                  | 84 |

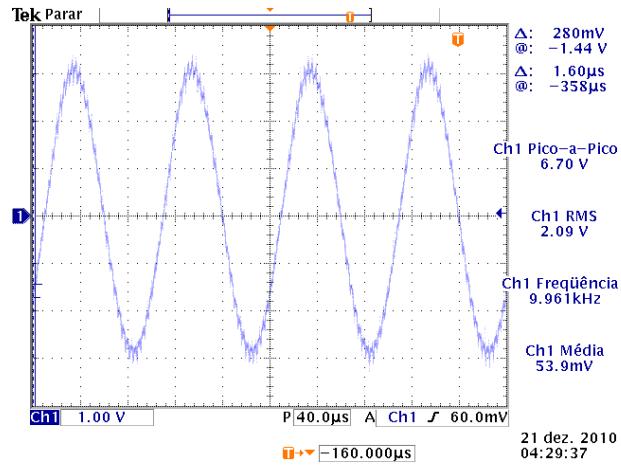

| 4.51 Sinal senoidal de saída a 10 kHz - malha aberta. . . . .                                                                                 | 84 |

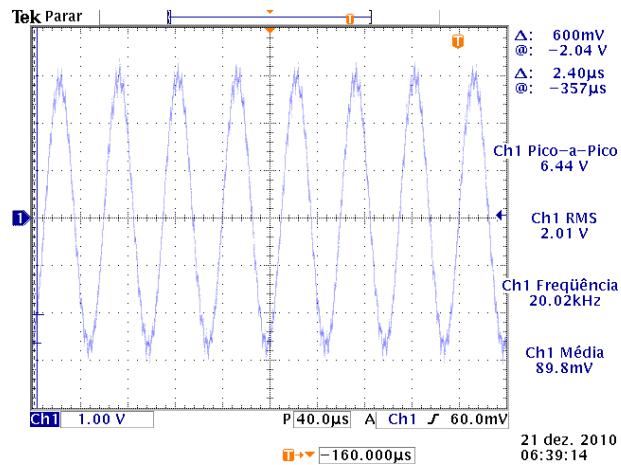

| 4.52 Sinal senoidal de saída a 17 kHz - malha aberta. . . . .                                                                                 | 85 |

| 4.53 Parâmetros utilizados no comparador para obter os resultados em malha fechada. . .                                                       | 85 |

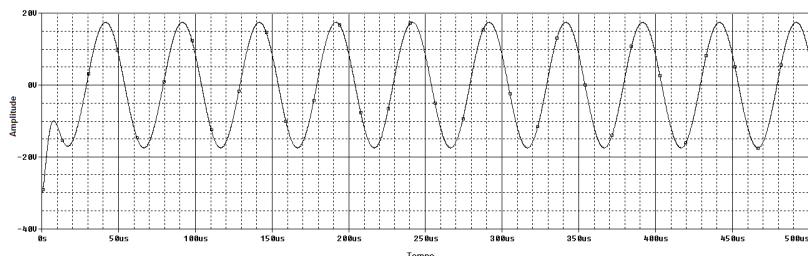

| 4.54 Sinal senoidal de saída a 20 Hz - malha fechada. . . . .                                                                                 | 86 |

| 4.55 Sinal senoidal de saída a 1 kHz - malha fechada. . . . .                                                                                 | 86 |

| 4.56 Sinal senoidal de saída a 10 kHz - malha fechada. . . . .                                                                                | 86 |

| 4.57 Sinal senoidal de saída a 20 kHz - malha fechada. . . . .                                                                                | 87 |

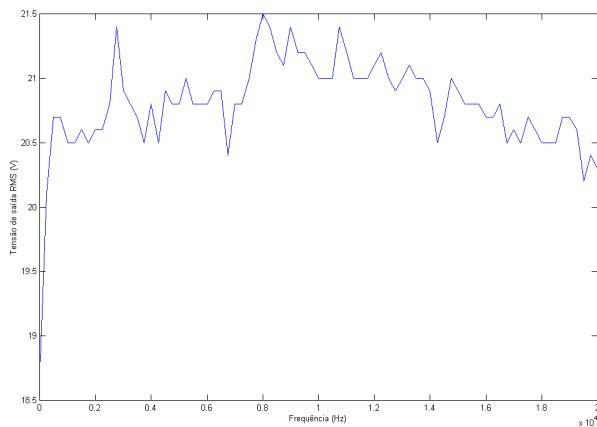

| 4.58 Tensão de saída RMS ao longo da banda audível. . . . .                                                                                   | 87 |

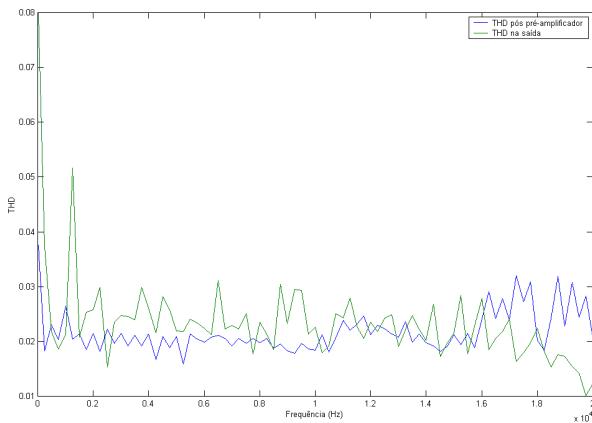

| 4.59 THD no sinal de entrada e saída. . . . .                                                                                                 | 88 |

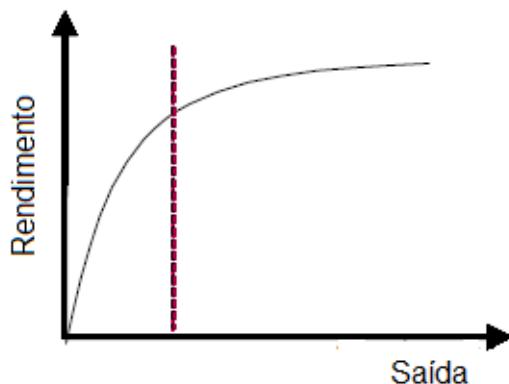

| 4.60 Curva típica de rendimento de um amplificador classe D. . . . .                                                                          | 89 |

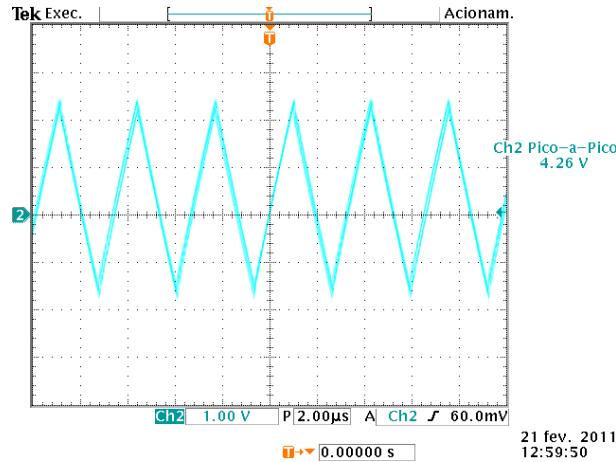

| 4.61 Correntes de magnetização nos indutores, para sinal de entrada nulo. . . . .                                                             | 90 |

| 4.62 Correntes de magnetização nos indutores de $80\mu H$ , para sinal de entrada nulo. . . . .                                               | 90 |

---

# **Lista de Tabelas**

---

|     |                                                                                |    |

|-----|--------------------------------------------------------------------------------|----|

| 2.1 | Comparativo entre topologias <i>Half Bridge</i> e <i>Full Bridge</i> . . . . . | 14 |

| 4.1 | Parâmetros utilizados nas simulações . . . . .                                 | 78 |

| 4.2 | Rendimento do amplificador . . . . .                                           | 89 |

---

## CAPÍTULO 1

---

# INTRODUÇÃO

---

O desenvolvimento de amplificadores de áudio remonta, do ponto de vista histórico, ao início do século XX. Com o advento da transmissão de rádio<sup>1</sup>, e o desenvolvimento de itens como o gramofone - um precursor arcaico dos aparelhos de LP -, a utilização de amplificadores de áudio passou a ser necessária. Isso porque a potência utilizada na transmissão de um sinal é muito pequena, em função da modulação utilizada pelo sinal, considerando ainda os efeitos de atenuação ocasionados pela atmosfera. O receptor, ao captar um sinal de rádio, por exemplo, precisa amplificar a mensagem recebida para criar um nível de potência sonoro adequado ao ouvinte.

Atualmente, com o avanço tecnológico e a integração cada vez maior de funcionalidades nos equipamentos eletrônicos, é possível encontrar amplificadores de áudio em praticamente qualquer dispositivo. Desde os tradicionais aparelhos de áudio, passando por televisões, computadores, computadores portáteis - *notebooks* - até dispositivos menores, como os *mp3 player* e celulares. É cada vez mais frequente as pessoas estarem utilizando recursos fornecidos por um amplificador de áudio de forma contínua, pois esta é uma das facetas da conectividade que os dispositivos de comunicação atuais fornecem. Além, é claro, de serem uma opção de lazer escolhida por muitas pessoas. Por exemplo, o tocador de mídias digitais *Ipod*, do fabricante *Apple*, atingiu a marca de 275 milhões de unidades vendidas, um valor altamente significativo [1]. Tais números demonstram que esta fatia do mercado segue uma tendência de crescimento acelerado.

Em suma, amplificadores de áudio vem sendo utilizados em uma gama cada vez maior de aplicações. Nos últimos anos, a grande expansão deu-se em aplicações portáteis, tais como celulares, *mp3 players* e similares. Esses dispositivos possuem características peculiares frente a sistemas de áudio de grande potência e qualidade. Pelo fato de serem portáteis, são dependentes de uma bateria e não podem ocasionar um gasto excessivo de energia, sob pena de minimizar o tempo de funcionamento do dispositivo. Contudo, amplificadores de áudio lineares - os mais populares - possuem desempenho pouco satisfatório, de no máximo 75%, para o caso de um amplificador classe AB [2]. Mesmo com essa limitação, os usuários desejam aparelhos com autonomia, qualidade no áudio e muitas vezes potência no mesmo. Apresenta-se, assim, um paradigma para os projetistas.

---

<sup>1</sup>Credita-se o desenvolvimento das comunicações via rádio ao italiano Guglielmo Marconi, em fins do século XIX.

Os circuitos amplificadores são utilizados há várias décadas como estágio de potência em diferentes aplicações [2, 3]. As configurações mais utilizadas, até hoje, são amplificadores lineares, dadas a sua simplicidade e desempenho satisfatório em boa parte das aplicações de áudio, sendo que a maior parte dos dispositivos de áudio utilizam amplificadores desta categoria [2].

Dentre os amplificadores lineares, o mais simples é denominado classe A. Apesar da ótima resposta linear, o amplificador apresenta um rendimento muito baixo, em torno de 25%, inviabilizando sua utilização para várias aplicações. Outra topologia, chamada classe B, aumenta o rendimento do circuito, porém introduz distorções no sinal amplificado - chamada de distorção *crossover*. A solução deste problema, por fim, está no chamado amplificador classe AB, que integra as melhores características dos modelos anteriores: uma eficiência superior, em torno de 75%, e eliminação dos problemas de distorção *crossover* [2–4]. Atualmente, a maior parte dos dispositivos de áudio domésticos integra amplificadores classe AB em sua constituição.

Contudo, mesmo com o predomínio dos amplificadores lineares até o momento, há outras classes de amplificadores disponíveis, tais como classe D, classe H, além de topologias híbridas [5]. A topologia classe D possui características particularmente interessantes. Ao contrário dos amplificadores lineares, nesta classe de amplificadores os transistores operam apenas em duas condições: em corte ou condução [2]. Por essa característica, tais amplificadores também são conhecidos como amplificadores chaveados. Por muitos anos sua aplicação em termos de áudio limitou-se a circuitos de *subwoofer* principalmente, ou seja, para amplificação de sinais de baixa frequência, no máximo da ordem de centenas de Hz [2, 6]. Isso ocorre devido a limitações impostas pela tecnologia, em função da modulação de áudio adotada por essa classe de amplificadores. Há dificuldades com relação à fidelidade sonora.

Pelo fato de os transistores funcionarem apenas em dois estados - em condução ou corte -, para haver amplificação do sinal de áudio o mesmo deve passar por uma modulação. No caso de amplificadores classe D, é comumente utilizada a modulação PWM - *Pulse Width Modulation* ou modulação por largura de pulso - [2, 6–15], que é gerada comparando o sinal de áudio com uma onda triangular ou dente de serra. O resultado da comparação são pulsos quadrados de largura variável, que são utilizados para acionar os transistores do estágio de potência. Este sinal PWM, amplificado, é capaz de reproduzir o sinal de entrada, após passar pela filtragem conveniente [16–18]. A modulação PWM exige, ainda, que a frequência com que haja a comutação dos transistores seja significativamente maior da frequência do sinal a ser amplificado, além de uma filtragem do sinal de saída para poder reconstituir o sinal original. No caso do áudio, espera-se uma frequência de modulação ao menos uma década maior do que a frequência de 20 kHz [4].

Então é possível depreender algumas ótimas vantagens e outras dificuldades no projeto deste tipo de amplificador. O grande ponto positivo é referente ao seu rendimento: normalmente superior a 90%, em função da operação dos transistores [2, 6]. Essa alta eficiência é o grande atrativo dessa classe, especialmente considerando o caso de aplicações portáteis, que exigem uma minimização do consumo de energia. Contudo, há a evidente desvantagem das não-linearidades introduzidas pela modulação PWM, que podem afetar o desempenho e a qualidade do aparelho

[7, 9, 10, 19]. Portanto, há de se ter uma atenção especial no projeto do circuito de controle e do filtro de saída para tentar contornar essas dificuldades. Contudo, o empecilho para uma maior popularidade dos amplificadores classe D, por muito tempo, foi decorrente da exigência de uma alta frequência de comutação nas chaves, devido à modulação PWM. Transistores bipolares, por exemplo, apresentam dificuldades para atuar em frequências da ordem de centenas de kHz. O advento dos MOSFETs, e posteriormente dos IGBTs, abriu novas possibilidades e possibilitou um grande desenvolvimento particularmente em aplicações que exigem chaveamento de transistores em altas frequências. Mas, dada a simplicidade de projeto de amplificadores classe AB, e de seu desempenho satisfatório, o uso de amplificadores classe D ficou limitado basicamente à aplicações em *subwoofer*, mesmo anos após o desenvolvimento de transistores com resposta veloz para o chaveamento - por volta da década de 1980.

Recentemente aumentou a demanda por aplicações de áudio em equipamentos portáteis, e os amplificadores classe D mostram-se como a opção mais promissora [2]. As dificuldades de projeto vêm sendo superadas, tanto com operação em frequências cada vez mais elevadas, como com a utilização de técnicas de controle adequadas, minimizando as distorções causadas pelas não-linearidades [19]. Hoje, portanto, é possível o projeto de um amplificador de áudio classe D de alta fidelidade sonora, podendo-se afirmar que a tendência é que essa classe seja, em poucos anos, predominante mesmo em relação aos amplificadores lineares [2]. Portanto, trata-se de um tema cujo interesse é crescente. É importante, contudo, a busca por técnicas cada vez mais adequadas, que permitam que amplificadores de áudio classe D sejam utilizados em maior escala. Nota-se que dois aspectos merecem maior atenção: possibilidade de incremento na frequência de operação do circuito, o que implica em possibilidade de maior fidelidade sonora e diminuição no tamanho dos componentes passivos do sistema, e também uma atenção ao circuito de controle.

Este trabalho apresenta uma contribuição para estes dois aspectos importantes em um amplificador classe D. É apresentada uma ampla revisão do conceito desta classe de amplificadores, justificando a crescente demanda por sua utilização atualmente. São apontadas as vantagens e desvantagens da topologia, e apresentada uma discussão desses problemas. São discutidas as diferentes formas de abordar os problemas, e serão apresentadas algumas soluções que permitem uma operação em frequências elevadas, minimizando as perdas, e uma discussão sobre modulação PWM em um inversor senoidal bipolar, e a viabilidade de sua utilização em um amplificador classe D.

É discutida a técnica da multiplexação de pulsos aplicada às chaves dos circuitos de potência - inversores e fontes chaveadas. Com essa abordagem, pretende-se facilitar a operação de circuitos de potência em frequências elevadas, possibilitando vantagens em termos de diminuição de componentes como filtros e indutores em um circuito. Também é verificada a relação entre a qualidade do sinal de saída do amplificador, medida por sua THD - *Total Harmonic Distortion*, distorção total harmônica -, em função do aumento da frequência do sinal modulante da modulação PWM. Também será verificado se, com o incremento na frequência de operação, há uma diminuição nas perdas, especialmente nas chaves, e consequente aumento de rendimento. É proposto um circuito de *driver* que atenda a essa demanda por alta frequência e ainda permita uma ampla flexibilidade, podendo acionar desde inversores às mais variadas topologias de fontes chaveadas. Outra proposta

da metodologia apresentada está no fato da minimização da necessidade da utilização de *snnubers* dissipativos para as chaves, em função da utilização da técnica de multiplexação dos pulsos.

Também há uma discussão sobre a utilização do inversor senoidal bipolar PWM para aplicações de áudio, e suas vantagens em termos de facilidade de implementação, controle, e eliminação de harmônicas. É verificada a possibilidade da utilização da técnica da multiplexação de pulsos em um inversor utilizado para amplificador de áudio classe D, bem como eventuais melhorias na qualidade do sinal de áudio amplificado em função da multiplexação realizada, e especialmente se há um incremento considerável no rendimento do circuito.

Outro aspecto importante, devido às não-linearidades da modulação PWM, é referente ao circuito de controle projetado. Tal aspecto, como mencionado, é fundamental para a qualidade do sinal gerado na saída do sistema, procurando maior fidelidade possível. Portanto, haverá uma revisão das técnicas de controle para a modulação PWM implementada para acionar o inversor do amplificador, bem como uma discussão de maneiras práticas de simplificar seus resultados, procurando aliar um circuito de alta performance com uma topologia simples, barata e robusta. É verificada a possibilidade de essa solução ser utilizada como um controle genérico de inversores, que sejam utilizados como amplificadores de áudio ou então em *no breaks* ou outras aplicações, com alteração apenas nos ganhos dos compensadores ao invés de mudança no projeto.

Este circuito de controle é composto por um compensador, e pode ser utilizado para o controle de um inversor utilizado em um amplificador de áudio como em um *no break*. Há também a possibilidade de sincronismo com outro amplificador de áudio análogo para a implementação de um sistema *stereo*. Outras características do controle proposto: *soft start*, pré amplificador simples porém com eficiência elevada, controle contra surtos de corrente, controle de temperatura.

Outro aspecto é que há, integrado ao mesmo projeto, um circuito de controle para conversores DC/DC, em sincronia com o controle do inversor. A primeira é uma topologia amplamente discutida na literatura [20, 21]. O objetivo é a montagem de uma placa de circuito de controle em que haja o circuito de controle do inversor, utilizado em amplificadores classe D, e do controle dos respectivos conversores que alimentam este circuito, em sincronismo. O desenvolvimento desses conversores, contudo, não está no escopo deste trabalho.

Existe, ainda, uma grande similaridade no projeto de um amplificador de áudio classe D com o de um *no break* monofásico utilizando amplificador da mesma classe. Basicamente, ambos consistem em um inversor, alimentado por fontes, para gerar um sinal de saída amplificado em relação a uma referência. No caso do *no break* faz-se a modulação de um sinal senoidal de 60 Hz - referência para gerar um sinal análogo ao da rede elétrica - ao invés de um sinal de áudio. Assim, o mesmo projeto de controle pode ser utilizado, com adaptações nos controladores e ajustes nas frequências de operação, para atuar em ambas as amplificações mencionadas. Também há possibilidade de alimentação do amplificador proposto por meio de baterias. Esta flexibilidade é importante em aplicações de áudio, especialmente visando aplicações automotivas.

Assim, este trabalho contém uma proposta de implementação de um amplifica-

dor classe D utilizando um inversor senoidal bipolar PWM multiplexado. É apresentada a técnica da multiplexação de pulsos para aplicação em inversores e fontes chaveadas, bem como o circuito desenvolvido para esta finalidade e seus respectivos resultados. Há uma revisão sobre os principais aspectos do inversor senoidal bipolar, e especialmente uma análise matemática da modulação PWM. Será feita uma ampla discussão do circuito de controle do inversor e do conversor, como também das demais partes do circuito de controle, como sincronismo, controle de temperatura e *soft start*. Este amplificador proposto pode ser utilizado tanto em aplicações de áudio como em *no breaks*, podendo ser alimentado por conversores alimentados pela rede elétrica ou por baterias. Além disso, para o caso da aplicação de áudio, o amplificador desenvolvido pode operar em toda a banda audível, de 20 Hz a 20 kHz, com qualidade no sinal de saída. Será mostrado que essa qualidade no sinal de saída está especialmente relacionada com a frequência utilizada na modulação PWM.

Sendo assim, o trabalho estruturar-se-á da seguinte maneira. Em um primeiro momento, há um capítulo dedicado à revisão da literatura sobre o tema, desenvolvendo as ideias que envolvem o projeto de amplificadores, bem como discutindo todos os conceitos abordados, desde a modulação PWM, a multiplexação dos pulsos no desenvolvimento do circuito de *driver*, e todo seu equacionamento, além da discussão dos filtros e métodos de controle, e de conceitos como THD. Também são apresentadas aqui as propostas para o desenvolvimento dos protótipos a serem testados. Há também um capítulo contendo resultados obtidos, que buscam validar boa parte das propostas. Para tanto, há uma série de simulações realizadas, em um primeiro momento, bem como o levantamento de alguns testes em *protoboard* de boa parte dos circuitos propostos, e resultados com os protótipos do circuito de *driver* multiplexado implementados. Também há os resultados obtidos com o protótipo inversor, em malha aberta e malha fechada. É feito o levantamento da potência obtida para a saída e de sua respectiva THD. Por fim, serão apresentadas as conclusões sobre os resultados obtidos, bem como sugestões para trabalhos futuros e uma eventual continuidade neste tópico de pesquisa. Espera-se realizar uma contribuição relevante no desenvolvimento de técnicas para incrementar a qualidade de projetos em amplificadores classe D, especialmente em aplicações de áudio, bem como abrir possibilidades para a continuidade das pesquisas efetuadas no âmbito de mestrado.

---

---

## CAPÍTULO 2

---

# REVISÃO DA LITERATURA

---

A ideia de se utilizar o conceito de chaveamento de transistores em amplificadores de áudio é antiga. O advento de transistores do tipo MOSFET tornou possível aplicações que utilizem comutações na ordem de centenas de kHz. Isso facilitou o desenvolvimento de fontes chaveadas. Em termos de amplificadores de áudio, os amplificadores lineares foram e continuam sendo largamente utilizados. Amplificadores do tipo A, B e AB estão presentes na maior parte dos dispositivos de áudio, especialmente devido às suas características de alta fidelidade - notavelmente no caso da classe AB. Contudo, para aplicações portáteis há inconvenientes. O maior problema é referente ao rendimento: dos amplificadores mencionados, o melhor rendimento é apresentado pelo classe AB, estando em torno de 78,5% [7].

Nesse sentido, amplificadores classe D mostram-se uma solução para muitas aplicações, especialmente áudio [2]. Eles utilizam técnicas de chaveamento para aplicar ganho de potência em um sinal de áudio. Portanto, do ponto de vista teórico, a eficiência alcançada seria 100% [7]. Na prática, a eficiência obtida normalmente é superior a 90% [15]. Pensando em componentes portáteis, dependentes de baterias, é fundamental que as aplicações possuam um elevado rendimento a fim de permitir uma maior durabilidade nas baterias. Também, em termos de tamanho do dispositivo, os amplificadores classe D tornam-se a melhor escolha pois seus componentes passivos, especialmente o filtro de saída, diminuem em função da maior frequência de operação [8].

Com a crescente demanda por portabilidade ocorrida ao longo dos últimos anos [12], os amplificadores classe D vem ganhando cada vez mais espaço no mercado de áudio, sendo utilizados em dispositivos de áudio portáteis, desde celulares a notebooks [2].

Contudo, há desvantagens em sua utilização. Como as chaves operam apenas na região de corte e saturação, a reprodução do sinal na saída do circuito é possível devido a utilização de técnicas de modulação. Comumente utiliza-se modulação PWM para essa finalidade [2, 6–10, 12–15]. Assim, a necessidade de utilização de um filtro de saída adequado torna-se um imperativo na maior parte das aplicações, com exceções em termos bem determinados [22]. Um projeto adequado de filtro é importante, por ocasionar redução nos custos, diminuir a interferência eletromagnética e

reduzir o ruído no sinal de saída, melhorando parâmetros como a Taxa de Distorção Harmônica - THD - [16].

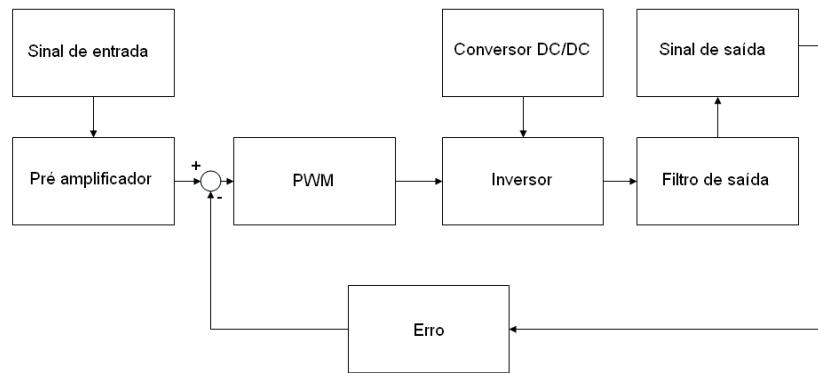

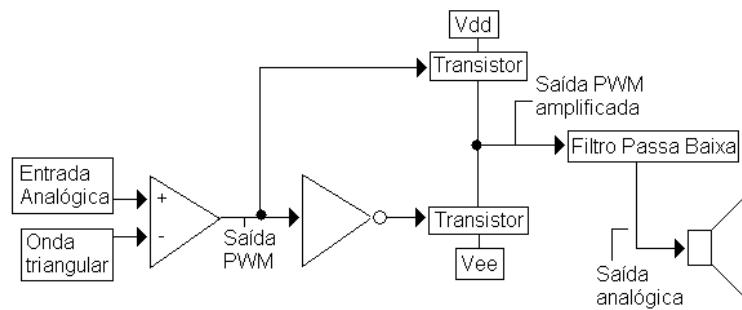

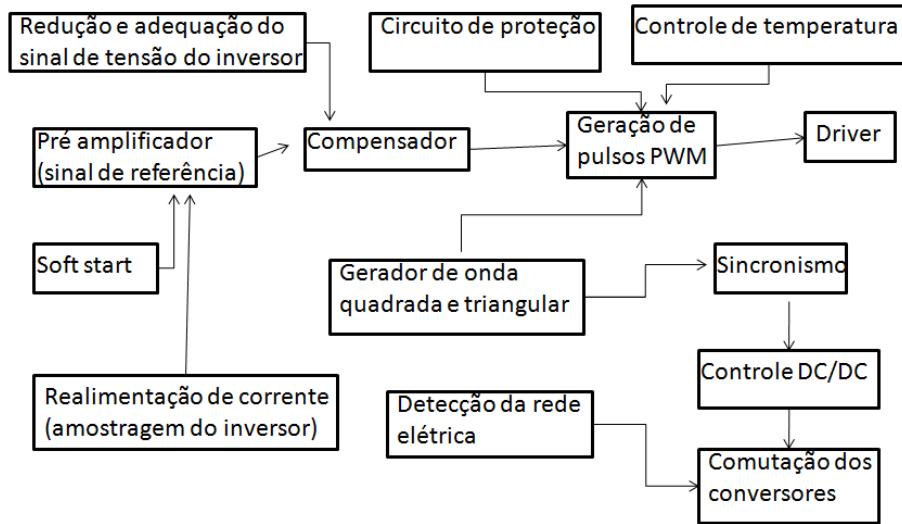

A figura 2.1 mostra um diagrama de blocos para o amplificador classe D proposto. Basicamente, o sinal de entrada é captado de algum aparelho de áudio, para o caso de aplicações de áudio, e passa imediatamente por um estágio pré-amplificador. Na sequência, este sinal é comparado com um sinal de erro, proveniente da saída do estágio inversor - responsável pela amplificação do sinal de áudio -, e comparado ainda com um sinal triangular para gerar um sinal PWM. Este sinal é responsável pelo acionamento das chaves do inversor, que por sua vez recebe potência de um conversor DC-DC. O sinal na saída do inversor é filtrado e, na saída do filtro, é possível recompor o sinal de entrada amplificado. O sinal de entrada pode ser uma referência senoidal a 60 Hz, para o caso do desenvolvimento de um *no break*

**Figura 2.1** – Diagrama de blocos para amplificador de áudio classe D proposto.

## 2.1 Parâmetros importantes no estudo de amplificadores de áudio

Em primeiro lugar, é importante definir uma série de conceitos e termos indispensáveis para a análise e estudo de amplificadores de áudio. Na sequência, há a apresentação e discussão desses conceitos.

### 2.1.1 Distorção

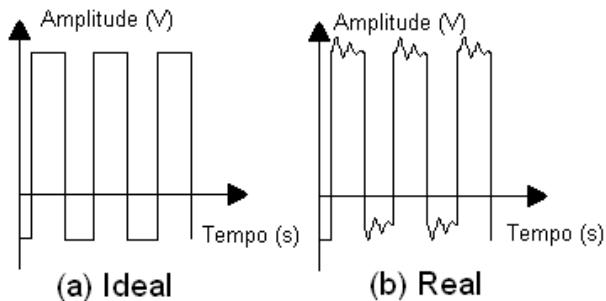

Idealmente, um amplificador de áudio realiza tão somente a amplificação e reconstituição do sinal de entrada original, com potência superior à entrada. Na prática, os dispositivos eletrônicos não são perfeitamente lineares, e introduzem deformações em relação ao sinal original. Vários fatores podem contribuir para este fenômeno: saturação de amplificadores, *slew rate* inadequado à operação, resposta em frequência inadequada dos componentes, dentre outros. Há dois parâmetros utilizados para a quantificação da distorção introduzida por um circuito: a Taxa de Distorção Harmônica (THD) e a distorção por intermodulação.

### Taxa de Distorção Harmônica - THD

A Taxa de Distorção Harmônica ou *Total Harmonic Distortion* (THD) de um circuito pode ser definida como segue, de acordo com a norma IEC 61000-2-2:

$$THD = \frac{\sum_{h=2}^{\infty} y_h^2}{y_1} \quad (2.1)$$

onde  $y_h$  é o valor eficaz total da  $h$ -ésima harmônica e  $y_1$  o valor eficaz da fundamental.

A norma permite limitar o valor  $h$  dos harmônicos em 50. Normalmente, o valor do  $THD$  vem expresso em porcentagem ou em  $dB$ . Para o caso de amplificadores de áudio, há o desejo de alta fidelidade, e portanto minimização da distorção. Pode-se considerar um dispositivo de alta fidelidade com  $THD$  em torno de  $-60dB$  ou melhor [13]. Em termos de porcentagem, pode-se afirmar que um amplificador de áudio de uso doméstico deve possuir  $THD \leq 0,1\%$  [23]. Em suma, a quantidade de harmônicos indesejados introduzidos pelas imperfeições do circuito devem ser muito baixos se comparados com a magnitude da fundamental.

### Distorção por intermodulação

Quando há duas ou mais frequências distintas no sinal de entrada, pode haver o surgimento de sinais com novas frequências resultantes de somas e subtrações das frequências originais, sendo tal fenômeno denominado distorção por intermodulação [24].

#### 2.1.2 Ruído

Ruído pode ser definido como um erro não presente no sinal de entrada, mas que aparece na saída do circuito independentemente da presença do sinal de entrada [24]. Ele pode ser causado pelo próprio circuito como por interferências eletromagnéticas externas, podendo ser de natureza aleatória - como o ruído térmico - ou determinística - sinais espúrios da rede elétrica, por exemplo. Uma medida importante, referente ao ruído, é a chamada relação sinal ruído (*Signal Noise Relation*, ou *SNR*).

### Relação Sinal Ruído - SNR

A relação sinal ruído (*Signal Noise Ratio* ou *SNR*) expressa a relação entre o sinal do amplificador e o ruído inserido, normalmente definida em  $dB$ :

$$SNR_{dB} = 20 \cdot \log\left(\frac{S}{N}\right) \quad (2.2)$$

onde  $S$  expressa a amplitude do sinal de interesse e  $N$  a amplitude do ruído.

Depreende-se que é interessante uma elevada SNR para o amplificador, por se tratar de uma quantificação do fato de haver pouco ruído em relação ao sinal de áudio, no caso de aplicações sonoras.

## 2.2 Amplificadores lineares de potência

Amplificadores de potência podem ser definidos simplesmente como um amplificador com estágio de saída em alta potência [3]. Para o caso de amplificadores de áudio, pode-se dizer que, a partir de pequenos sinais, fornecem grandes sinais a cargas de baixa impedância, resultando em elevadas correntes e potência de saída [4].

As classes de amplificadores de potência são determinadas em função da forma de onda de corrente no coletor (para o caso de utilização de transistor bipolar) ou dreno (para MOSFET) que resulta da aplicação de um sinal de entrada [3]. Algumas dessas classes de amplificadores mais comuns em aplicações de áudio são: classe *A*, classe *B*, classe *AB* e classe *D*. Tradicionalmente, em aplicações de áudio, utiliza-se muito amplificadores das classes *B* e *AB*, especialmente, sendo que amplificadores classe *D* tem ganhado espaço ultimamente no mercado [2].

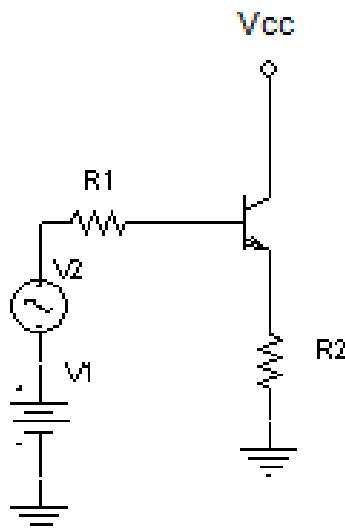

### 2.2.1 Amplificador classe A

Amplificadores classe *A* possuem, como característica primordial, uma corrente de polarização mais elevada que o sinal de corrente amplificado. O transistor, então, conduz durante todo o ciclo do sinal de entrada, e seu ângulo de condução é  $360^\circ$ . Assim, trata-se de uma configuração menos complexa, mais linear e com menor distorção harmônica para sinais de pequenas amplitudes [4].

**Figura 2.2** – Amplificador classe A.

O rendimento máximo desse estágio de saída é de 25%. Portanto, raramente é utilizado em aplicações de alta potência, superiores a 1 W [3]. A figura 2.2 apresenta um esquema de um estágio de saída classe A.

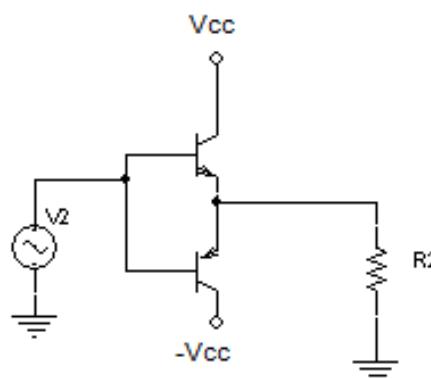

### 2.2.2 Amplificador classe B

O arranjo básico dessa topologia é mostrado na figura 2.3 e implica que as chaves jamais conduzirão simultaneamente. O rendimento dessa configuração é, em média, de 50%, porém com uma maior distorção no sinal em relação ao amplificador classe A.

**Figura 2.3** – Amplificador classe B.

**Figura 2.4** – Distorção de *crossover*.

Ao contrário do estágio apresentado anteriormente, cada transistor no amplificador classe B conduz em um período do sinal de entrada sendo que seu ângulo de condução é, no máximo, 180°. Ou seja, os dois transistores jamais conduzirão em conjunto. Devido a essa característica surge um fenômeno importante a ser destacado: a distorção *crossover*. Ela aparece em função do intervalo que ocorre entre os instantes de condução de ambos os transistores. Ou seja, há um breve instante em que nenhum dos transistores conduz, mesmo havendo um sinal de entrada. Isso introduz uma não-linearidade no sinal de saída. A figura 2.4 exemplifica esse fenômeno. Em um amplificador de áudio isso dá origem a um som desagradável [3].

Assim, apesar da vantagem em relação ao rendimento frente o amplificador classe A, o amplificador classe B é inadequado para aplicações que exigem alta fidelidade sonora, devido à existência de distorção de *crossover*.

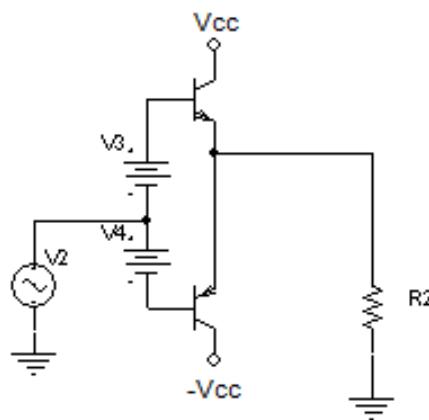

### 2.2.3 Amplificador classe AB

O amplificador classe AB faz uma síntese das melhores características dos amplificadores classe A e classe B: alta fidelidade sonora e incremento no desempenho, minimizando perdas. A ideia é minimizar a distorção de crossover permitindo que ambos os transistores da configuração conduzam simultaneamente quando a tensão do sinal estiver próxima a 0 V, por um breve período de tempo. Na prática, isso significa que no momento em que um dos transistores deixa de conduzir, o outro começa seu estágio de condução. Para tanto, há a necessidade de uma pequena tensão de polarização para cada chave, como mostrado na figura 2.5.

**Figura 2.5 – Amplificador classe AB.**

Devido a essas características, que permitem uma baixa taxa de distorção no sinal aliada a um rendimento satisfatório para boa parte das aplicações [2, 6], essa classe de amplificadores é ainda hoje a mais comum para projetos de amplificadores de áudio.

### 2.3 Amplificador classe D

A ideia básica do amplificador de áudio classe D é, ao contrário das demais topologias apresentadas, funcionar com os transistores operando apenas na região de corte ou saturação, utilizando a mesma ideia das fontes chaveadas. A vantagem desse procedimento de operação é o elevado rendimento, idealmente 100%, e na prática superior a 90% [2, 6]. Como as chaves atuam em apenas dois níveis de tensão, para haver a reprodução do sinal de entrada na saída é necessário a utilização de alguma técnica de modulação. O mais comum é a utilização da modulação PWM, mas outras podem ser utilizadas, com desvantagens, como por exemplo a modulação sigma-delta [2].

A figura 2.6 apresenta um diagrama simplificado do funcionamento de um amplificador de áudio classe D. Basicamente, uma entrada analógica passa, primeiramente, por um estágio de modulação PWM, através de uma comparação com um sinal triangular ou dente-de-serra. No exemplo, a figura apresenta um estágio *half-bridge* na saída, com apenas dois transistores para o estágio de potência. Ambos são excitados com pulsos PWM complementares, gerando um novo sinal PWM em seu estágio de saída, porém amplificado em relação ao primeiro. Esses transistores de potência constituem um inversor [25], responsáveis pela conversão do nível de tensão DC fornecido pelos conversores DC/DC em um tensão alternada, no caso o sinal PWM amplificado. A topologia apresentada, com duas chaves apenas, é chamada *half-bridge*. Assim, basta filtrar o sinal oriundo do inversor e inseri-lo na carga - no caso, um alto-falante. Para o estágio de potência também poderiam ser utilizados quatro transistores na topologia inversora, implementando uma topologia *full-bridge*.

**Figura 2.6 – Amplificador classe D.**

Portanto, os amplificadores classe D possuem, como vantagem, seu alto rendimento, superior a 90%. Contudo, em relação às topologias anteriores, possui a desvantagem de menor linearidade e possíveis distorções no sinal de saída do amplificador, o que é sempre indesejado em um amplificador de áudio. Todavia, atualmente é possível obter amplificadores classe D de alta fidelidade [2, 19], o que faz com que seu uso em diferentes aplicações seja cada vez mais comum. Essa alta fidelidade é possível utilizando frequências mais elevadas para a modulação PWM, por exemplo, e com um projeto adequado para o filtro de saída.

### 2.3.1 Considerações sobre o rendimento e THD

Vários aspectos explicam os motivos de o rendimento, na prática, estar em torno de 90%. Dois deles são os principais: os tempos de comutação não nulos dos transistores utilizados bem a resistência de condução dos transistores, chamadas de  $R_{on}$ . O primeiro aspecto traz consigo uma consequência negativa: a inserção de um tempo entre os pulsos que acionam as chaves no inversor. Tal procedimento é necessário para evitar que pulsos complementares acionem chaves distintas em conjunto por um breve intervalo de tempo, o que significaria um curto-círcuito na fonte que alimenta o inversor. Na prática, esse é um parâmetro crítico na THD de um amplificador classe D. Um tempo morto de 40 ns cria uma THD de 2%, enquanto 15 ns acarretaria em 0,2% de THD [26].

Isso implica um cuidado na escolha dos semicondutores a serem utilizados, pri-

mando por componentes que comutem na ordem de dezenas de ns, bem como possuam baixa  $R_{on}$ . Isso para assegurar maior eficiência aliada a um desempenho de qualidade.

Há outras causas secundárias que podem implicar em um rendimento inferior ou queda na qualidade do sinal de saída. Eventuais erros ou dificuldades na geração dos pulsos PWM e não-linearidades nas capacitâncias e indutâncias do filtro de saída também podem ter relação com o rendimento e a THD do circuito, bem como variações na tensão de alimentação do circuito de potência do amplificador [27].

### 2.3.2 Detalhamento das perdas nos MOSFETs

O aspecto crítico para o rendimento em um amplificador classe D são as perdas nas chaves - MOSFETs [26, 27]. A relação que define as perdas em um amplificador classe D é dada pela equação (2.3), obtida de [27]:

$$P_{total} = P_{sw} + P_{cond} + P_{gd} \quad (2.3)$$

O termo  $P_{sw}$  é a perda nas chaves e é definido por:

$$P_{sw} = C_{oss} \cdot V_{BUS}^2 \cdot f_{PWM} + I_D \cdot V_{DS} \cdot t_f \cdot f_{PWM} \quad (2.4)$$

Na equação (2.4),  $C_{oss}$  é um parâmetro intrínseco do semicondutor,  $V_{BUS}$  é a tensão do barramento,  $f_{PWM}$  é a frequência da modulação PWM indicada,  $I_D$  é a corrente no dreno e  $t_f$  o tempo de desligamento do MOSFET.

O termo  $P_{cond}$  são as perdas de condução:

$$P_{cond} = \frac{R_{DS(ON)}}{R_L} \cdot P_O \quad (2.5)$$

Por fim,  $P_{gd}$  são as perdas no *driver*:

$$P_{gd} = 2 \cdot Q_g \cdot V_{gs} \cdot f_{PWM} \quad (2.6)$$

sendo  $Q_g$  um parâmetro intrínseco do MOSFET relacionado à capacitância do *gate*.

Dessa forma, é impossível identificar que as perdas em um amplificador classe D estão majoritariamente relacionadas à perdas nos MOSFETs. Ou seja, a escolha de chaves adequadas à aplicação é fundamental para minimizar as perdas no circuito. A frequência de operação do circuito também possui relação direta com as perdas: quanto maior a frequência, maiores as perdas, e consequentemente o desempenho tende a diminuir.

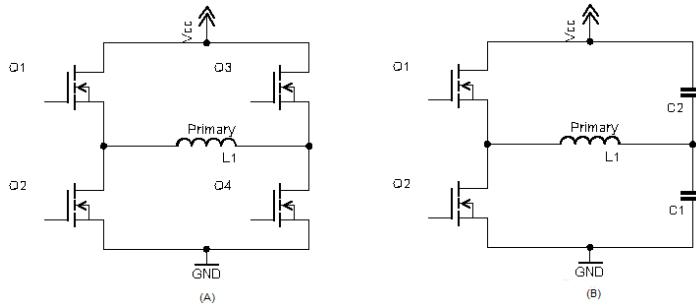

### 2.3.3 Topologias inversoras utilizadas: *Half Bridge* ou *Full Bridge*

A tabela 2.1 apresenta um comparativo entre as características da topologia *Half Bridge* e um conversor *Full Bridge*:

**Tabela 2.1 – Comparativo entre topologias *Half Bridge* e *Full Bridge***

| Característica              | <i>Half Bridge</i>                     | <i>Full Bridge</i>                                       |

|-----------------------------|----------------------------------------|----------------------------------------------------------|

| Corrente nas chaves         | $I_{média} = I_{entrada}$ (cada chave) | $I_{média} = \frac{1}{2} \cdot I_{entrada}$ (cada chave) |

| Tensão sobre as chaves      | $V_{cc}$ para cada chave               | $V_{cc}$ para cada chave                                 |

| Número (mínimo) de MOSEFETs | 2                                      | 4                                                        |

| Número de <i>drivers</i>    | 2                                      | 3                                                        |

| <i>Offset DC</i>            | Requer ajuste                          | Pode ser eliminado                                       |

| Padrão PWM                  | 2 níveis                               | 2 ou 3 níveis                                            |

| Realimentação               | Necessária                             | Pode ser utilizado em malha aberta                       |

Vê-se que, apesar de custo mais elevado, devido ao maior número de componentes, a utilização da topologia *Full Bridge* traz muitas vantagens na montagem de um amplificador classe D, tais como semicondutores com corrente nominal inferior (mais baratos) e maiores possibilidades na implementação do amplificador (circuito de controle, modulação PWM, etc.). A figura 2.7 (A) apresenta um comparativo esquemático entre ambas as topologias. Em 2.7 (A) há uma topologia *Full Bridge*, enquanto em 2.7 (B) um exemplo de topologia *Half Bridge*.

**Figura 2.7 – (A) Topologia *Full Bridge* e (B) Topologia *Half Bridge*.**

A grande vantagem da topologia *Full Bridge* é a possibilidade de se utilizar a modulação unipolar (3 níveis ou modulação BD, que será descrita a seguir juntamente com suas vantagens).

### 2.3.4 Outras topologias

Há ainda outras topologias utilizadas em amplificadores classe D, porém em menor escala. Um exemplo é a seguinte topologia, apresentada na figura 2.8 [6, 28]. As vantagens desta topologia é que não exige fonte de alimentação estável, como a maioria das topologias desta classe, bem como prescinde de um filtro passa-baixas na saída do circuito.

Outras vantagens desta topologia podem ser citadas. Em primeiro lugar, o número reduzido de chaves - duas -, que implica em menores custos inclusive pela diminuição do número de

**Figura 2.8** – Topologia de amplificador classe D - dispensa filtro de saída.

*drivers* exigidos por uma topologia *Full Bridge*, por exemplo. Além disso, há uma significativa redução de EMI, pois a comutação suave é naturalmente obtida, e não há necessidade de *snubbers* dissipativos nas chaves.

### 2.3.5 Conclusões

Há várias topologias possíveis para utilização em amplificadores de áudio classe D. De um modo geral, é importante notar a grande vantagem desta classe de amplificadores em termos de rendimento: nenhum outro tipo de amplificador pode alcançar um rendimento tão elevado. Atualmente, estes amplificadores tem dominado o mercado de áudio, já sendo utilizados em variadas aplicações de áudio, e não apenas *subwoofer* [2, 19]. Por exemplo, amplificadores classe D já são uma tendência dominante em aplicações automotivas. As recentes aplicações alcançam um desempenho adequado em termos de distorção.

Em relação à outras classes de amplificadores, o amplificador classe D exige um projeto de maior complexidade para alcançar resultados proporcionais aos obtidos com amplificadores lineares. Esse é um dos motivos pelos quais esses últimos ainda são utilizadas em larga escala na indústria.

Das topologias apresentadas, cada uma apresenta suas particularidades, contando a favor ou contra a sua escolha. Para este trabalho, a opção é por uma topologia *Full Bridge*, para verificar a viabilidade da utilização de uma modulação bipolar (AD) em alta frequência de frequência de operação, bem como verificar o comportamento do filtro de saída em malha fechada.

## 2.4 A modulação PWM

A técnica de modulação PWM - *Pulse Width Modulation* ou Modulação por Largura de Pulso - é amplamente utilizada em amplificadores de áudio classe D [2, 6–14], como também é normalmente utilizada para o acionamento das chaves em fontes chaveadas [29]. Consiste em permitir apenas dois estados para a chave, em nível alto ou baixo, sendo que no caso de um conversor a potência de saída é dada em função da variação da largura do pulso. A grandeza que define a relação entre o tempo em que o pulso está em nível lógico alto e nível baixo chama-se razão cíclica e é definido como sendo:

$$D = \frac{t_{(on)}}{T} \quad (2.7)$$

Na equação (2.7)  $t_{(on)}$  é o tempo em que o pulso permanece em nível lógico alto e  $T$  é o período total do pulso, como mostrados na figura 2.9. A modulação PWM baseia-se, essencialmente, na variação da largura dos pulsos em função da comparação de um sinal analógico com algum sinal de referência - um dente-de-serra ou uma onda triangular.

A modulação PWM permite [25]:

- Assegurar a variação da amplitude da componente fundamental da tensão de saída, sem distorcer a forma de onda;

- Redução das harmônicas de menor ordem, facilitando a filtragem das componentes parasitas.

**Figura 2.9** – Pulso quadrado e os parâmetros da razão cíclica.

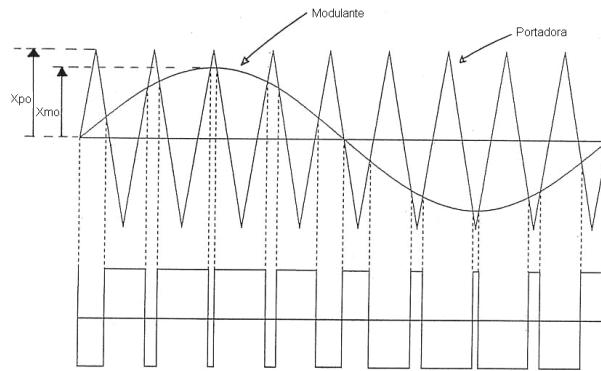

Há diferentes técnicas para realizar uma modulação PWM analógica. O ponto importante para a escolha é aquela modulação que gera um sinal com menor conteúdo harmônico. Essa característica é importante, pois tende a facilitar o processo de filtragem do sinal [19]. O primeiro aspecto a determinar um conteúdo harmônico maior ou menor é a forma de onda utilizada na modulação: onda triangular ou dente-de-serra. A literatura disponível já discutiu o tema [19], de modo que é seguro afirmar que, em termos de componentes harmônicos na saída, a melhor escolha é pela utilização de uma onda triangular.

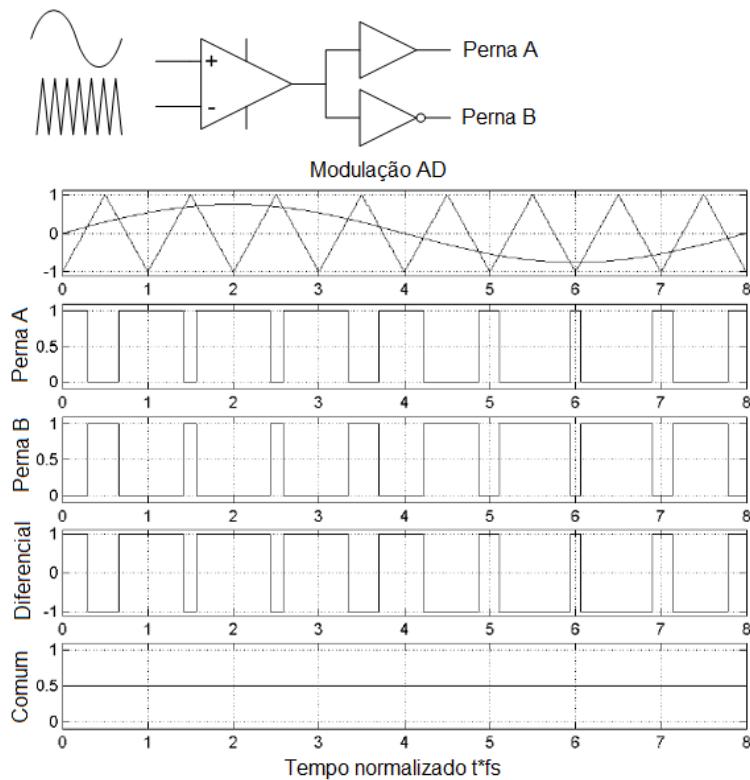

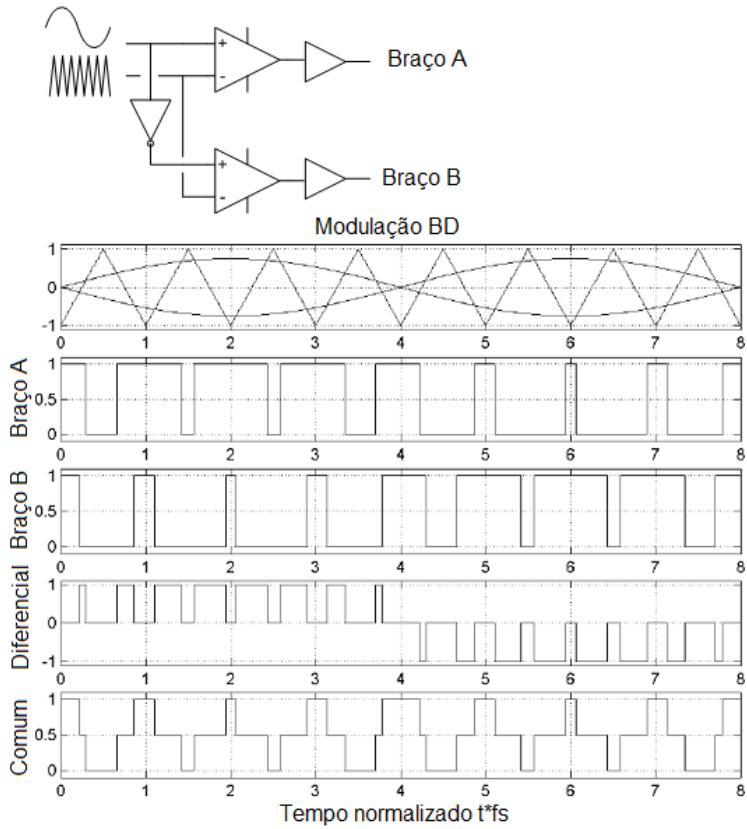

Além disso, há dois tipos de esquema para gerar o sinal PWM:

- Modulação AD (ou bipolar): esquema tradicional com uma saída diferencial, sendo cada saída defasada em  $180^\circ$  da outra. A amplitude de cada um desses pulsos varia, sempre, de um valor de referência 0 V ao valor  $V_{cc}$ . A saída diferencial, antes da filtragem, contudo, varia entre valores de  $-V_{cc}$  a  $V_{cc}$ , ou seja, dois níveis de saída. A grande tensão diferencial pode causar picos de corrente na saída, aumentando as perdas no filtro de saída.

- Modulação BD (ou unipolar): esquema no qual as variações da tensão diferencial de saída alternam entre, sempre, entre 0 V e  $\pm V_{cc}$ , ou seja, três níveis de saída. Em alguns casos pode haver eliminação da necessidade de filtro de saída [17].

**Figura 2.10** – Esquema de geração e formas de onda da modulação AD, adaptação.

A figura 2.10 apresenta o esquema necessário para implementar a modulação AD, enquanto a figura 2.11 o esquema necessário para modulação BD, ambas as figuras adaptadas de [17]. As figuras permitem evidenciar as diferenças entre ambos esquemas de modulação. Com relação à saída diferencial, nota-se os dois níveis existentes na modulação AD em detrimento dos três níveis da modulação BD. Já a saída de modo comum é constante para a modulação AD e variável para modulação BD.

Há diferenças na elaboração dos filtros de saída em ambos os casos. A figura 2.12 apresenta o esquema a ser implementado para um filtro em um circuito utilizando modulação AD,

**Figura 2.11** – Esquema de geração e formas de onda da modulação BD, adaptação.

enquanto a figura 2.13 um esquema semelhante, mas para modulação BD [17]. Nota-se, para o caso da modulação AD, a necessidade de um capacitor em paralelo com a carga.

As conclusões obtidas em [19], em relação aos diferentes tipos de modulação, são importantes e merecem atenção. Em primeiro lugar, a modulação utilizando onda triangular ao invés de onda dente-de-serra apresenta componentes de distorção por intermodulação consideravelmente menores. Também possui um conteúdo harmônico com metade das componentes presentes em uma modulação utilizando onda dente-de-serra.

Define-se o índice de modulação  $M$  como sendo:

$$M = \frac{\Delta f}{f_m} \quad (2.8)$$

Na equação (2.8),  $\Delta f$  é a diferença entre a frequência da portadora em relação ao modulante, e  $f_m$  a frequência do modulante.

A modulação AD é interessante apenas com sua utilização por meio de um índice de modulação elevado, ou seja, com portadora de frequência elevada. No capítulo 4 deste trabalho são apresentadas simulações que buscam indicar um valor satisfatório para esses valores.

**Figura 2.12** – Filtro de saída para modulação AD.

**Figura 2.13** – Filtro de saída para modulação BD.

Os resultados obtidos em [19] indicam que normalmente a utilização de modulação BD com sinal triangular como portadora na obtenção da modulação PWM é a melhor escolha. Esta técnica apresenta os melhores resultados em termos de sinal diferencial, apesar de apresentar um sinal de modo comum significantemente superior ao apresentado no caso da modulação AD. Contudo, a obtenção da modulação BD é mais complexa do que a modulação AD, conforme pode ser observado nas figuras 2.10 e 2.11. Além disso, indica-se que a utilização de um índice de modulação elevado permite a utilização da modulação AD com resultados satisfatórios [19]. A técnica da multiplexação de pulsos, proposta neste trabalho, permite obter um índice de modulação elevado, de modo verificar o comportamento da modulação AD nestas condições.

#### 2.4.1 Descrição analítica da modulação PWM

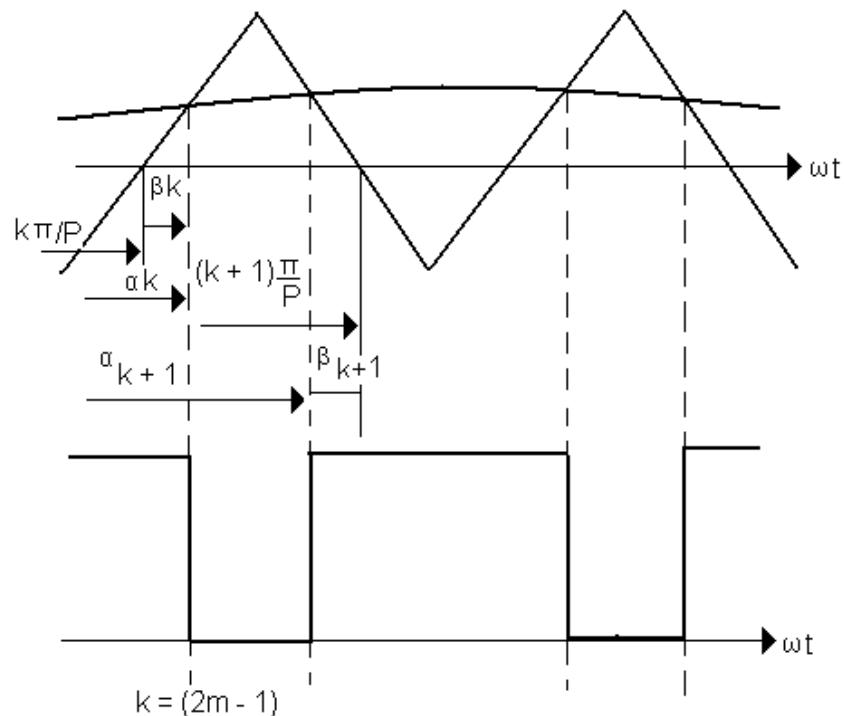

Uma descrição do PWM é mostrada a seguir [25]. Para o caso de um inversor, e considerando a figura 2.14 - adaptada de [30] -, as comutações possuem uma anti-simetria entre as alternâncias positivas e negativas (referentes ao sinal senoidal) e simetria em relação a um quadrante do período (do sinal senoidal), eliminando harmônicas pares. Portanto:

$$u(\omega t) = -u(\omega t + \pi) \quad (2.9)$$

e

$$u\left(\frac{\pi}{2} - \omega t\right) = u\left(\frac{\pi}{2} + \omega t\right) \quad (2.10)$$

onde a função  $u(\omega t)$  descreve a tensão de saída de um inversor, por exemplo.

**Figura 2.14** – Geração de um sinal PWM por meio de modulação senoidal, adaptação.

A modulação PWM de implementação mais simples é a assíncrona de dois níveis [25], utilizada neste trabalho - trata-se da modulação AD. Na prática, para este caso, não é possível realizar uma decomposição das harmônicas da tensão de saída. Contudo é possível realizar uma decomposição sensivelmente próxima para o caso de uma modulação síncrona. Portanto, será feita a análise deste caso.

A modulação síncrona é obtida pela comparação entre dois sinais: um modulante e uma portadora. O modulante pode ser um sinal senoidal ou uma forma de onda de áudio, por exemplo, e a portadora, que pode ser tanto de tipo dente-de-serra quanto triangular, possui frequência angular  $\omega_p$  sendo múltiplo ímpar da modulante  $\omega$ . Na figura 2.14 tem-se uma frequência de portadora nove vezes maior daquela do modulante.

Define-se o índice de pulsação  $P$  como sendo:

$$P = \frac{\omega_p}{\omega} = 2K - 1$$

sendo:

$$K \in [1, 2, 3, \dots]$$

Define-se também as funções  $f_1(\omega t)$  e  $f_2(\omega t)$ , que caracterizam os estados dos braços do inversor. Essas funções estão defasadas entre si de um semi-ciclo de onda, ou seja, são

pulsos complementares entre si. Cada braço do inversor é acionado por um sinal representado por essas funções.

### 2.4.2 Análise da tensão de saída

A tensão de saída, aqui denominada  $u$ , pode ser decomposta em série de Fourier como segue:

$$u = \sum_{j=1}^{\infty} (u)_{(2j-1)M} \sin[(2j-1)\omega t] \quad (2.11)$$

com:

$$u_{(2j-1)M} = \frac{2}{\pi} \int_0^{\pi} u \sin[(2j-1)\omega t] d\omega t = \frac{4}{\pi} \int_0^{\frac{\pi}{2}} u \sin[(2j-1)\omega t] d\omega t \quad (2.12)$$

Não é possível obter uma expressão analítica para as componentes harmônicas de  $u$ . Definem-se os ângulos  $\alpha_k$  - cujos valores são raízes de equações transcendentais<sup>1</sup> - para os instantes de comutação, conforme a figura 2.15.

**Figura 2.15** – Definição dos instantes de comutação.

<sup>1</sup>Equações transcendentais não apresentam solução que possa ser expressa através de funções elementares. Ou seja, é necessário recorrer ao cálculo numérico para solucioná-la.

Com isso, é possível escrever:

$$\alpha_k = k \frac{\pi}{P} + (-1)^{k-1} \beta_k \quad (2.13)$$

sendo  $\beta_k$  definido como:

$$\beta_k = \frac{\pi}{2P} \frac{X_{mo}}{X_{po}} \sin \left[ k \frac{\pi}{P} + (-1)^{k-1} \beta_k \right] \quad (2.14)$$

Os parâmetros  $X_{mo}$  e  $X_{po}$ , presentes na equação 2.14, são, respectivamente, a amplitude do modulante e a amplitude da portadora, conforme apresentados na figura 2.14. Uma solução analítica aproximada é possível se o intervalo:

$$\left[ \frac{-\pi}{2P} + k \frac{\pi}{P}, \frac{\pi}{2P} + k \frac{\pi}{P} \right]$$

com  $k \in [0, 1, 2, \dots]$ , que possa tornar semelhante  $\sin \omega t$  a  $\sin \frac{k\pi}{P}$ .

Nestas condições, é possível obter:

$$u_{(2j-1)M} = \frac{4U}{(2j-1)\pi} \left\{ 1 - \sum_{k=1}^{\frac{P-1}{2}} (-1)^k \cos \left[ (2j-1) \left( k \frac{\pi}{P} \frac{X_{mo}}{X_{po}} \sin \left( k \frac{\pi}{P} \right) \right) \right] \right\} \quad (2.15)$$

A simplificação no modulante equivale a uma discretização do sinal. Ou seja, nos casos em que o sinal PWM é obtido digitalmente, a equação (2.15) é precisa. Ainda é possível obter algumas constatações referente às harmônicas. Em primeiro lugar, a amplitude da fundamental de  $u$  pode ser entre 0 e 78% para o caso do comando por onda quadrada - quando a amplitude da portadora é igual a do modulante [25]. É possível dizer que a modulação PWM de uma senóide em uma onda triangular acarreta em harmônicos de baixa ordem que podem ser eliminados. Lembrando razão de modulação de frequência, definida na equação (3.1), é possível ainda dizer que as principais harmônicas geradas pela modulação PWM, além da fundamental, estão em frequências em torno do índice de modulação [31]. Por exemplo, para índice de modulação  $M_f = 10$ , as principais harmônicas geradas estão nas frequências  $(M_f \pm 2) \cdot f_r$  e  $(M_f \pm 4) \cdot f_r$ , onde  $f_r$  é a frequência do sinal de entrada do inversor. Isso demonstra a eficácia da utilização de um filtro passa-baixas para recompor o sinal de entrada em um inversor utilizado em um amplificador de áudio classe D, recompondo apenas a fundamental com certa facilidade.

# DESENVOLVIMENTO

---

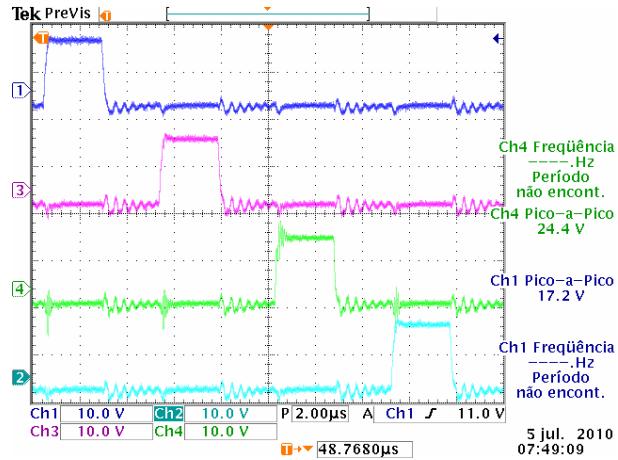

## 3.1 Circuito inversor

Os inversores são utilizados para gerar uma tensão alternada a partir de uma tensão contínua, sendo seu uso principal em *no-breaks*, acionamento de motores e amplificadores de áudio [31]. O trabalho em questão apresenta uma proposta de um amplificador de áudio classe D, sendo, portanto, o projeto do inversor uma das principais etapas do trabalho. Aliado a isso, há a necessidade de utilizar um filtro na saída do inversor, de modo a eliminar as harmônicas no sinal de saída gerado, e assim poder recompor o sinal de entrada com maior fidelidade possível, atentando-se a parâmetros como a taxa de distorção harmônica (THD).

A topologia proposta é um inversor senoidal bipolar PWM, com chaves multiplexadas. A modulação PWM gera pulsos de largura variável para o acionamento das chaves, o que permite a eliminação de várias harmônicas em relação a uma modulação por onda quadrada, por exemplo [25, 31]. A descrição do funcionamento da modulação PWM será feita na seção 2.4. Com relação à topologia inversora proposta, já amplamente discutida na literatura [20, 21, 25, 31], a novidade é a presença da técnica da multiplexação dos pulsos, que possibilita que o inversor trabalhe em uma maior frequência de operação, influindo decisiva e positivamente no desempenho do projeto de um amplificador de áudio [2, 6, 16, 22] e contribuindo para uma redução no tamanho dos componentes passivos do sistema (indutores, transformadores), especialmente no filtro de saída.